【工程师分享】MicroBlaze大内部存储器(AXI BRAM)设计

judy 在 周四, 06/17/2021 - 09:54 提交

MicroBlaze可以使用AXI BRAM存放数据和指令。有些客户软件很大,需要把AXI BRAM的空间做到最大。AXI BRAM底层是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM个数,决定了AXI BRAM的大小。

MicroBlaze可以使用AXI BRAM存放数据和指令。有些客户软件很大,需要把AXI BRAM的空间做到最大。AXI BRAM底层是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM个数,决定了AXI BRAM的大小。

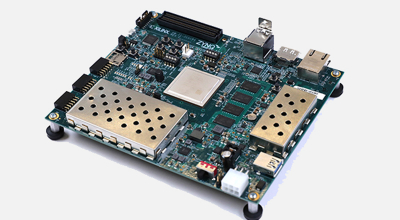

Lewis Rhodes Labs NPUsearch 网络取证设备 - 将搜索时间从数小时缩短至数分钟

Alveo系列开发板上的平台其实是一个DFX设计的静态部分,在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel, 最终这些Kernel的逻辑会在分布在DFX设计的动态区域。本篇将介绍如何为Kernel的逻辑做floorplan(画Pblock),人为控制Kernel逻辑的布局。

Kria K26 SOM 旨在帮助数百万开发人员在其首选设计环境中使用开箱即用的低成本开发套件更快地部署他们的智能视觉应用程序。

Zynq® UltraScale+™ MPSoC 是 Xilinx 最新的 SoC 片上系统系列之一。这些器件将实时控制与软硬引擎相结合,为图形、视频、波形和数据包处理提供了 64 位处理器可扩展性。三款不同型号均基于常用的实时处理器和可编程逻辑平台

本视频演示如何通过 Vitis 统一软件平台访问 Zynq® UltraScale+™ RFSoC 的文档,其中包括 API 和示例文件。

现在大规模FPGA的bitstream比较大导致板卡从上电到FPGA配置完成的时间远远超过100MS的要求,从而电脑端无法正常识别到PCIE设备。为此Xilinx的PCIE Tandem功能是专为满足PCIe设备在100ms之内枚举起来要求而设计的。

本视频说明了如何消除由 C 设计中的阵列引起的瓶颈。

近日GTIC 2021嵌入式AI创新峰会在北京圆满收官!作为下午场唯一家硬件平台厂商代表,赛灵思公司的软件和解决方案市场部高级经理刘珊珊带来了以《MPSoC平台加速工业视觉应用创新》为题的深入分享。

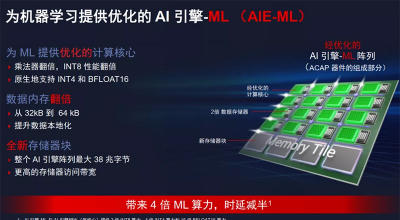

近几年,边缘计算市场在快速增长,速度超过了数据中心。有统计显示,到2025年,边缘AI芯片的市场机遇是数据中心的3倍,规模将达到650亿美元。这样具有巨大发展潜力的市场,是所有能够参与到其中的芯片厂商特别关注的,无论是CPU、GPU,还是FPGA。作为FPGA行业龙头,赛灵思也已经准备好推出相应的器件