【视频】Vivado 2020.2 中的新增功能(中文字幕)

judy 在 周三, 06/09/2021 - 09:32 提交

本视频着重介绍了 Vivado Design Suite 2020.2 版中的新增功能,包括操作系统和器件支持、高级别增强功能以及加速设计集成、实现与验证相关的各项改进措施。

本视频着重介绍了 Vivado Design Suite 2020.2 版中的新增功能,包括操作系统和器件支持、高级别增强功能以及加速设计集成、实现与验证相关的各项改进措施。

调频连续波(FMCW)光雷达的原型验证和测试面临着许多挑战。接下来让我们一起探讨,对这些挑战进行分解,使其变得可管理且可付诸行动,并学习有关如何逐步克服组件级到系统级测试挑战的实用指南。

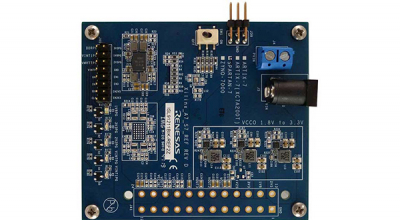

瑞萨电子的 Xilinx FPGA 参考板是一个扩展电源,旨在为 Xilinx Artix-7、Spartan-7 和 Zynq-7000 系列提供各种 Xilinx 电源。插墙式 AC/DC 适配器或台式直流电源可通过板上的桶式插座给该板供电。

Linux是现在最流行的操作系统,含有大量的源代码。Xilinx 2020.1使用的Linux 5.4,含有大约67430个文件。大部分文件没有被使用到。分析Linux源代码的代码实现时,经常查找函数或者数据结构定义。如果分析所有文件,既消耗软件查找时间;也会找到多个定义,增加理解代码的难度

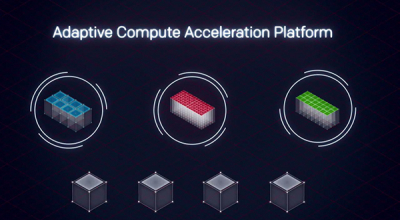

本视频通过不到一分钟的时间介绍了自适应计算加速平台。这是一项了不起的创新,它将异构加速的强大功能与软件和芯片可编程特性结合在一起。 ACAP 将为任何应用和任何开发人员提供一个平台,帮助他们去革新计算领域的格局。

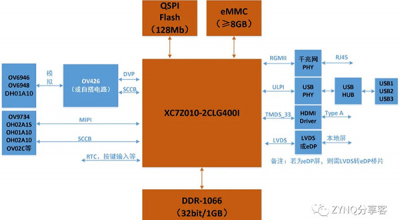

这一次,熊猫君分享一个内窥镜的技术实现方案。内窥镜的方案很多:主处理器有用专用ASIC的,比如日、台、韩的相机ASIC;有用专用CPU的,比如海思、瑞星微和君正等。熊猫君的这个是基于Xilinx ZYNQ的低成本方案。

每个 RPU 处理器都有 1 个 DBGDSAR 寄存器,其中包含其 CoreSight ROM 表的偏移地址。但是,读取 RPU 的 DBGDSAR 寄存器会返回以下不正确的偏移值:

当赛灵思首次出现在以汽车为主题的Auto Tech 2021展会时,它显示出两个强烈的信号:1、自动驾驶的市场热度开始进入一个新的拐点;2、为数不多的拥有先进典型处理架构的芯片巨头正在加快在汽车领域跑马圈地的节奏。

本视频介绍如何使用赛灵思FPGA为数据库工作负载和分析负载提速。

Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado 2020.2为例,讨论如何升级Vivado工程脚本。