终于等到你!Xilinx 展台如约而至,三大板块圈粉AUTO TECH 2021!

judy 在 周二, 05/25/2021 - 14:03 提交

5月的羊城,一路盛开的火红的凤凰花,似乎在代表广州这个年产汽车中国第一的城市,热情迎接来自全国各地的Auto Tech 展商及观众。赛灵思及合作伙伴技术与商务专家云集羊城,希望借助 Auto Tech 这样的行业平台和广州深厚的产业影响力,让赛灵思面向下一代的智能驾驶开发平台和解决方案,赋能更多的创新者。

5月的羊城,一路盛开的火红的凤凰花,似乎在代表广州这个年产汽车中国第一的城市,热情迎接来自全国各地的Auto Tech 展商及观众。赛灵思及合作伙伴技术与商务专家云集羊城,希望借助 Auto Tech 这样的行业平台和广州深厚的产业影响力,让赛灵思面向下一代的智能驾驶开发平台和解决方案,赋能更多的创新者。

在PYNQ RFSoCWorkshop之后,Xilinx再次推出DSP-PYNQ,与之前只发布了基于RFSoC2x2开发套件的overlay和notebooks不同,本次发布的工程增加了对ZCU111和Ultra96的支持。

本答复记录旨在描述在 Versal ACAP 器件上使用物理不可克隆功能 (Physically Unclonable Function,PUF) 时,与 VCC_PMC 电源轨相关的要求。

本视频讨论功耗约束以及报告功耗估算的最佳实践。

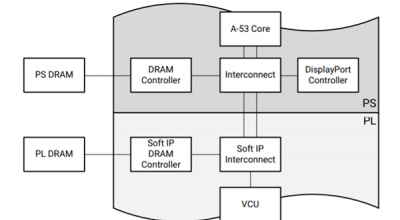

Xilinx提供超低延时编解码方案,并提供了全套软件。MPSoC Video Codec Unit提供了详细说明。其中的底层应用软件是VCU Control-Software(Ctrl-SW)。本文主要说明为Ctrl-SW增加功能,支持不同Stride/Pitch(步长)的YUV文件的编码。

在某些条件下,新负载如果复用旧器件负载的分组标识 (GID),则可能报告同步外部异常中止,原因是错误关联旧器件存储器访问所检测到的外部错误。器件负载快速解析完成,并允许后续指令执行时复用 GID。

本视频将讲解提高结果质量的最新方法窍门与技巧。

Lower操作完成从高级算子(relay)到低级算子(TOPI)的转化。Lower开始于以下代码(src/relay/backend/graph_runtime_codegen.cc)

Xilinx提供超低延时编解码方案,并提供了全套软件。MPSoC Video Codec Unit提供了详细说明。其中的底层应用软件是VCU Control-Software(Ctrl-SW)。本文主要说明为Ctrl-SW增加输出NV12视频的功能。