【线上技术峰会】与16位国内外顶级大师相约Xilinx Adapt China:数据中心专场

judy 在 周二, 05/11/2021 - 17:43 提交

在这为期三天的线上会议,您将了解赛灵思如何破解种种难题,实现完整软件定义和完整硬件加速的数据中心加速。您将看到来自行业头部运营商的成功部署案例;赛灵思合作伙伴的交钥匙解决方案;赛灵思最新的数据中心战略和技术。从而帮助您解决棘手的数据中心挑战。

在这为期三天的线上会议,您将了解赛灵思如何破解种种难题,实现完整软件定义和完整硬件加速的数据中心加速。您将看到来自行业头部运营商的成功部署案例;赛灵思合作伙伴的交钥匙解决方案;赛灵思最新的数据中心战略和技术。从而帮助您解决棘手的数据中心挑战。

Vivado HLS工具支持C/C ++浮点和双精度数据类型,它们基于IEEE-754标准定义的单、双精度二进制浮点格式。浮点数值格式由于精度有限不能表示每个实数。

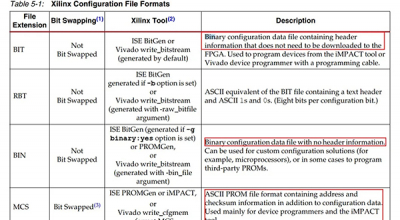

FPGA里面的可执行文件都涉及到 *.bit, *.mcs, *.bin 和 *.elf,到底都有什么用,应该怎么用呢,这篇文章小编会简单介绍下这几种文件。

本视频重点讨论动态功能交换Dynamic Function eXchange

MPSoC的MAC支持1588。在Linux Kernel的配置项中使能CONFIG_MACB_USE_HWSTAMP,并在Linux rootfs添加Linux ptp/ethtool,就可以运行1588的软件命令ptp4l。

如果用户设计在可编程逻辑中明确强制使用数据 IMUX 寄存器,那么逻辑函数可能不正确。IMUX 寄存器旨在用于进行 Vivado 自动时序最优化。Vivado 设计工具会在时序最优化期间对 IMUX 寄存器进行相应管理,以避免发生此错误。

SmartLynq+ 模块教程视频介绍了如何在 Versal ACAP 设计中包括高速调试端口,并演示了 SmartLynq+ 模块配置和 Linux 映像下载流程。

JTAG是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS(测试模式选择)、TCK(测试时钟输入)、TDI(测试数据输入)、TDO(测试数据输出)

在测试MPSoC VCU的编解码时,经常需要使用NV12 YUV文件。YUV文件很大,所以经常依靠解压MP4等文件来产生NV12 YUV文件。 FFMpeg是一个强大的工具,可以用来从MP4文件生成NV12 YUV文件。