开发者分享 | 调试 FFT C-Model 仿真和 FFTIP 前仿

judy 在 周五, 03/12/2021 - 14:16 提交

有很多客户在比较 FFT C-Model 仿真和 FFTIP 前仿遇到问题。今天赛灵思技术专家对此提出三种原因和解决办法。

有很多客户在比较 FFT C-Model 仿真和 FFTIP 前仿遇到问题。今天赛灵思技术专家对此提出三种原因和解决办法。

在 v2020.2 中,针对 AXI 主接口引入了 Vitis HLS 自动接口扩展选项,了解如何与使用端口上的矢量数据类型来显式描述端口宽度进行比较。

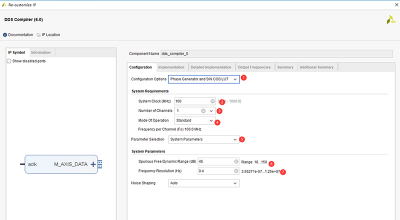

本次项目我们主要是为了讲解DDS,所以我们使用了混频这个小项目来讲解。DDS自己手写是比较简单且灵活,但是Xilinx给我们提供了相应的IP核,那么这次我们将直接讲解使用IP来产生不同频率的正弦波

国家政策导向逐步明确;5G发展进一步加速;云计算、大数据迎来又一波发展高峰.........这些因素都注定推动了数据中心产业的转型升级。对于数据中心转型,单从软件或硬件层面中的一个层面下手发力远远不够,需要企业“软硬兼施”,双管齐下,才能在数据中心转型升级的过程中,抢占先机,平顺、快速、完美的完成转型升级。

电源估算工具随 VCK190/VMK180 评估套件提供,是一款允许用户最大限度提高功耗性能比的生产力工具。有了该工具,用户可测量、规划和监控整个开发过程中的电源预算,不会影响在 Versal ACAP 上运行的设计。电源工具是开发板评估与管理 (BEAM) 工具的一个特性,其可为 Versal 评估套件用户提供更高的创造性体验。

vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。今天介绍的是Vivado的三种常用IP核

本文描述了Xilinx®Alveo™SN1000 SmartNIC的规范。

示波器的需求急速成长,同时新的研究和测试应用也需要更多、更快、更复杂的讯号。 这会需要更具智能功能的测试设备,才能准确侦测特定的讯号状况并避免空滞时间、在采集期间处理资料以缩短测试时间,或者是快速产生反馈讯号以控制待测装置 (DUT)。 过去十年来,强大 PC 软件和模块化 I/O 的紧密整合,不仅缩短了测试时间,同时也降低了整体测试成本

赛灵思 Alveo 加速器卡具备低时延性能和大规模并行处理能力,为构建这些关键应用提供了理想的基础。赛灵思日前推出了一款基于 Alveo 的 AI 视频分析平台。它具备合作伙伴解决方案生态系统,并且专为最复杂、时延最敏感的 AI 视频推断应用提速而打造。

IBERT(Integrated Bit ErrorRatio Tester,集成误比特率测试工具),是Xilinx提供用于调试FPGA高速串行接口比特误码率性能的工具,最常用在GT高速串行收发器测试:

(1)基于PRBS模块的误码率测试;

(2)测量眼图;