【视频】最大化广播带宽:基于感兴趣区域(ROI)的编码

judy 在 周三, 02/10/2021 - 10:37 提交

本视频将演示使用Zynq UltraScale+ MPSoC视频编解码单元,实现基于感兴趣区域的编码,并将其用于广播带宽最大化。

本视频将演示使用Zynq UltraScale+ MPSoC视频编解码单元,实现基于感兴趣区域的编码,并将其用于广播带宽最大化。

Free RTOS实时操作系统运行环境,这里不深入探讨Free RTOS的具体使用。本实验以FreeRTOS Hello World做举例,并实现两个LED灯以不同间隔持续闪烁。本实验基于 “PL端AXI GPIO的使用”工程,硬件环境不需要修改。

本指南提供新版本的 Vivado® Design Suite 概述,包括有关新增功能和功能变更信息、软件安装需求以及许可信息。其中还提供了已知问题列表,并包含指向可提供最新信息的答复记录的链接。

SmartLynq+模块是一个高速调试和跟踪模块,主要面向Versal ACAP用户。在本视频中,我们将介绍SmartLynq+模块的主要功能和接口,它能够提供更强大的器件编程、软硬件调试、性能分析以及事件跟踪功能。

Xilinx官方为大家提供了很多IP核,在Vivado的IP Catalog中可以查看这些IP核,用户在构建自己的系统中,不可能只使用Xilinx官方的免费IP核,很多时候需要创建属于自己的用户IP核

FSM有限状态机,是FPGA和数字IC相关岗位必须要掌握的知识点,在笔试和面试中都非常常见。

本文描述了如何在Versal™设备上使用高级I/O向导构建源同步高速I/O接口。

赛灵思宣布正为富士通( Fujitsu Limited ) O-RAN 5G 射频单元( O-RU )提供领先的 UltraScale+ 技术。采用赛灵思技术的富士通 O-RU 将部署在美国首个符合 O-RAN 标准的新建 5G 网络中。与此同时,富士通正对赛灵思 RFSoC 技术进行评估,以期为后续更多基站的部署进一步降低成本和功耗。

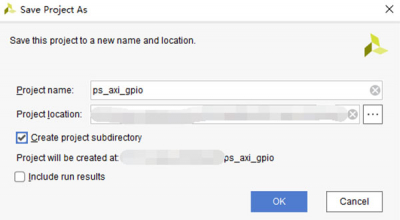

前面讲过如何用的是PS端的EMIO点亮PL端LED灯,但是并没有与PL端产生交互。本章介绍另外一种控制方法,在ZYNQ当中可以使用AXI GPIO,通过AXI总线控制PL端的LED灯。同时也介绍了PL端按键的使用。

鉴于DNN 在研究和技术方面的巨大投资,很明显,DNN 作为首选解决方案的适用范围,将会继续迅速扩大。然而,在可预见的未来,许多应用将通过传统技术(包括其他形式的机器学习)或通过深度学习和传统算法的组合,来获得最好的解决方案。接下来,我们就一起了解一下,深度学习在机器视觉中的典型应用。