Xilinx与大陆集团联合打造汽车行业首款用于自动驾驶的量产版 4D 成像雷达

judy 在 周四, 09/24/2020 - 14:58 提交

赛灵思和大陆集团今日宣布将通过 Zynq® UltraScale+™ MPSoC 平台支持大陆集团开发新款高级雷达传感器 (ARS) 540,联手打造汽车行业首款量产版 4D 成像传感器

赛灵思和大陆集团今日宣布将通过 Zynq® UltraScale+™ MPSoC 平台支持大陆集团开发新款高级雷达传感器 (ARS) 540,联手打造汽车行业首款量产版 4D 成像传感器

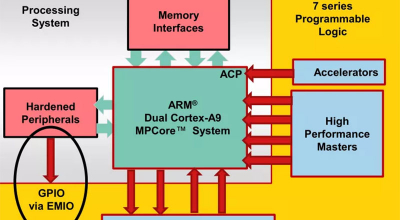

ZYNQ架构:双核ARM Cortex-A9 处理器:ARM Cortex-A9 是一个应用级的处理器,能运行完整的像Linux 这样的操作系统,传统的现场可编程门阵列(Field Programmable Gate Array,FPGA)逻辑部件:基于Xilinx 7 系列的FPGA 架构

Messaging Classification Appliance(消息分类工具)由 Xilinx 和 Supermicro 合作推出,是一种预封装的软件和硬件解决方案,可通过理解语义内容(消息的含义和意图)实时大规模地过滤、分类和路由消息流。

赛灵思将通过 Zynq® UltraScale+™ MPSoC 平台支持大陆集团开发新款高级雷达传感器( ARS ) 540,联手打造汽车行业首款量产版 4D 成像传感器。双方的合作将助力配备 ARS540 的新车型实现 SAE J3016™ L2 功能,为迈向 L5 自动驾驶系统铺平道路。

芯快递联合贸泽工程师社区为大家送上中秋国庆好礼啦~~

活动时间:即日起截止到2020年9月30日(数量有限,不容错过!)

这次的福利活动,我们将送出的好礼是Cypress Semiconductor CY8CKIT-040 PSoC 4000 Pioneer开发套件,它支持开放式平台,通过板载针座实现对 PSoC 4000 设备的完整访问,支持 Arduino™ 硬件。

我们将随机抽出4名幸运儿,送出我们的开发套件一套。

注意:获得开发套件的小伙伴,需要写一篇该开发套件的评测文章哦,标题自拟。

赛灵思为 FPGA 和 MPSoC 器件中所有受支持的 I/O 标准提供了 I/O 缓存信息规范 (I/O Buffer Information Specification, IBIS) 模型。本篇博文旨在提供有关如何为可编程逻辑 (PL) 和处理器系统 (PS) 多用途 I/O (MIO) 进行 IBIS 模型名称解码的指导信息。

FZ3是米尔与百度紧密合作推出的一款基于Xilinx Zynq Ultrascale CZU3EG芯片打造的深度学习计算卡,芯片内部集成了4核ARM A53处理器+GPU+FPGA的架构,具有多核心处理能力、FPGA可编程能能力以及视频流硬件解码能力等特点

移动互联网时代,每时每刻都在产生大量的图像和视频内容,内容提供商面临的主要问题是如何实现对内容的有效过滤,避免不允许的内容被公开。睿视演示了一种基于AI+FPGA的图像过滤方法,使用Xilinx Alveo加速器卡对特定图片/视频内容进行有效实时过滤。

几个常用的 AXI 接口 IP 的功能(上面已经提到):

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换

AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<----->AXI-Stream 的转换

本应用说明提供了一个包含控制逻辑的模块,用于将SMPTE UHD-SDI与UltraScale™ GTH收发器耦合,形成一个完整的UHD-SDI接口。本应用说明还提供了一个在Xilinx UltraScale FPGA KCU105评估板上运行的SDI设计示例。