PYNQ经典项目分享| 可重配置IO

judy 在 周二, 06/23/2020 - 10:06 提交

PYNQ-PRIO是一个介绍如何利用FPGA部分可重配置特性和PYNQ框架提供的方便的API,对FPGA分时复用,提高FPGA灵活性的项目。可重配置是指在一个FPGA工程中,划分了静态逻辑部分和动态逻辑部分,静态逻辑部分是指在运行过程中逻辑不变的部分

PYNQ-PRIO是一个介绍如何利用FPGA部分可重配置特性和PYNQ框架提供的方便的API,对FPGA分时复用,提高FPGA灵活性的项目。可重配置是指在一个FPGA工程中,划分了静态逻辑部分和动态逻辑部分,静态逻辑部分是指在运行过程中逻辑不变的部分

Xilinx 功耗估计器 (XPE) 是一个基于电子数据表的工具,旨在帮助您进行功耗估算。XPE 可在设计周期的任何阶段估算设计功耗。它将通过简单的设计向导来获取设计信息,同时对这些信息进行分析并提供详尽的功耗和热性能信息。

一个工程师打算在命令行里编译Xilinx SDK工程,以便集成进入其它自动化构建工具。Xilinx SDK工程都支持在命令行编译。在命令行里编译Xilinx SDK工程前,需要执行call C:/Xilinx/SDK/2019.1/settings64.bat,设置编译环境。

Xilinx® Alveo™ U30 是一款基于 PCIe 的小尺寸媒体加速卡,可为实时流媒体视频服务提供商、OEM 厂商以及内容分发网络 (CDN) 提供高密度的实时转码解决方案。U30 加速器卡随 Xilinx 实时视频服务器一体机参考架构 (高通道密度版)同时推出,由 Xilinx 的 OEM 和 VAR 合作伙伴提供。

本文演示了使用Vivado®Design Suite和Vitis™软件平台构建基于Zynq®-7000SoC处理器的嵌入式设计。提供有效的嵌入式系统设计教程。

Xilinx 7系列FPGA内置了一个模数转换模块,称为XADC。XADC内部集成了两个最高1MHz采样率,1Vpp的ADC模块,可以采集FPGA外部输入的模拟信号并转为数字信号。XADC不需要外接任何输入信号,就可以测量FPGA内部的温度,VCCINT,VCCBRAM,VCCAUX电压。

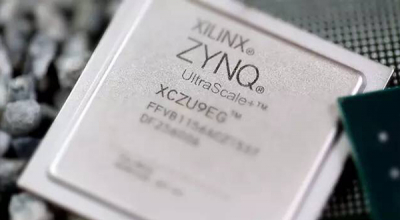

当我们打算进行ASIC或是SoC原型验证的时候, FPGA或许是我们最好的选择。各大厂商正努力提升工艺水平,制造拥有更高逻辑密度和更大I/O 数量的FPGA。Xilinx 未来将要上市的VU19P拥有 900 万个系统逻辑单元,为搭建当今最复杂 SoC与ASIC的原型与提供了条件。

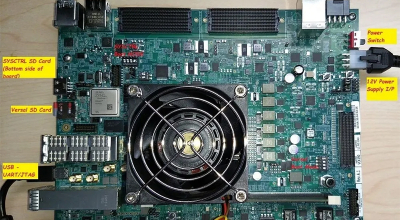

Versal™ ACAP(自适应计算加速平台)是高度集成化的多核计算平台,可通过灵活的自适应能力来满足不断变化的动态算法的需求。VCK190 是赛灵思最早发布的 Versal AI Core 评估器件之一。本篇博文将为您详解如下所述设计创建步骤:

本文介绍MPSoC的芯片启动流程

本白皮书探讨如何将 Xilinx® Vivado® HLS 环境中开发的现有 HLS 设计移植到 Mentor 的 Catapult® HLS 平台中。