Vitis尝鲜(一)

judy 在 周五, 03/20/2020 - 11:12 提交

vitis虽然已经发布很长时间了,但是我就要尝鲜。。。首先是安装,本教程分两个主要的平台(WIN10和Ubuntu)给出安装教程和源文件。

vitis虽然已经发布很长时间了,但是我就要尝鲜。。。首先是安装,本教程分两个主要的平台(WIN10和Ubuntu)给出安装教程和源文件。

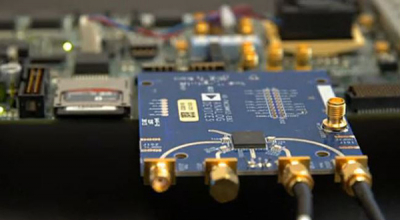

ADC芯片会包含许多性能参数,而我们在选择ADC芯片时,其中有一项关键性的参数值得关注,即数字化的数据输出接口类型(the type of digital data output)。目前在高速ADC芯片中,使用最广泛的数据输出接口类型有3种

本篇文章来测试Tutorials中的第2个例子:Mixing C++ and RTL Kernels。该例子中进行了两个步骤的实验,分别是sw_emu和hw_emu,我这变还是会继续在硬件上直接测试。

得益于西班牙电信和赛灵思的努力,包括VR / AR媒体产品,到互联汽车和工业IoT设备的丰富的无线服务,将在整个欧洲比预期更早实现。这家跨国电信运营商,今天宣布,将赛灵思与多家业界领先的软硬件公司联合在一起,以期冲击市场并加速其 4G 和 5G 无线网络中 O-RAN 技术的发展。

本视频由 Baicells(佰才邦) 在 2019 MWC 上展示其面向 NR 加速及同步的 O-RAN 和 TIP Open RAN PCIe 加速卡,以及面向 O-RAN 的室内 Radion Hub。

作者:bt_

原文链接: https://blog.csdn.net/botao_li/article/details/103901856

* 本文由作者授权转发,如需转载请联系作者本人

主要参考:ug1400

安装串口调试软件

安装串口软件 tinyserial

本人使用 Qt 5.12.6 编译后使用(deb 安装后无法运行)。

建立 Platform Project

在实时性要求较高的场合中,CPU软件执行的方式显然不能满足需求,这时需要硬件逻辑实现部分功能。要想使自定义IP核被CPU访问,就必须带有总线接口。ZYNQ采用AXI BUS实现PS和PL之间的数据交互。本文以PWM为例设计了自定义AXI总线IP,来演示如何灵活运用ARM+FPGA的架构

基于JESD204数字接口的数据转换器正在兴起,目前渐渐取代了部分基于LVDS接口的数据转换器,这种趋势就如同十几年前基于LVDS接口的数据转换器开始取代基于CMOS接口的数据转换器情形一样。

阿里云的业务之一是为众多第三方厂商处理海量产品图像。由于一些图像内含有未付费广告等多余文本信息,给付费广告业务造成不利影响,因此,为了确保电子商务网站提供一致的体验,需要以 AI 推断对每天数千万幅图像中嵌入的有害文本或多余文本进行检测

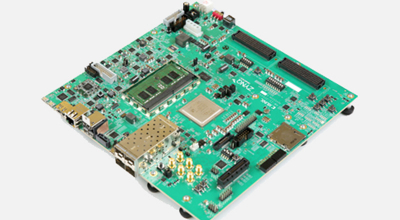

Vitis 被 Xilinx 称为 “统一软件平台”,从目前已了解的情况来看,嵌入式软件开发在 Vitis 上更为简单方便。从 ISE 到 Vivado,再到 Vitis 的升级趋势来看,Vitis 将是未来数年的开发主力。