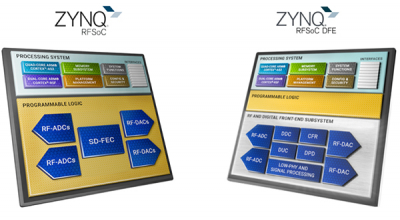

Zynq UltraScale+ RFSoC器件介绍

judy 在 周一, 05/22/2023 - 14:43 提交

本文介绍一下Xilinx公司新一代Zynq UltraScale+ RFSoC器件

本文介绍一下Xilinx公司新一代Zynq UltraScale+ RFSoC器件

本实验主要介绍使用PS端来完成ZYNQ串口打印输出的功能

通过XTmrCtr_GetValue获取时间戳,是以时钟周期为单位的

本文介绍利用TI公司TXS0108实现FPGA IO Bank接不同外设IO接口电压转换

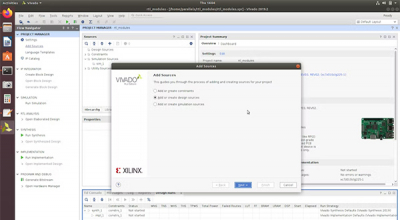

使用Vivado Block Design设计解决了项目继承性问题,但是还有个问题,不知道大家有没有遇到

Xilinx 7系列FPGA IO Bank分为HP Bank和HR Bank,HP IO接口电压范围为1.2V~1.8V

如何在 FPGA 中进行简单和复杂的数学运算。

FPGA中的Bank和Clock Region有什么关系?这应该是很多FPGA工程师都很困惑或者没有认真相关的一个问题

本文重点介绍cache在FPGA中的实现方案

Corundum是一个基于FPGA的开源NIC原型平台,用于高达100Gbps及更高的网络接口开发