Vivado中IP核的Core Container特性

judy 在 周二, 10/10/2023 - 09:25 提交

本文将介绍Vivado中XCI与XCIX文件以及如何使用Core Container打包IP核

本文将介绍Vivado中XCI与XCIX文件以及如何使用Core Container打包IP核

复位是将某个系统或者设备恢复到预先指定的状态

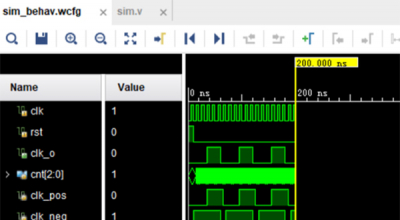

本文将介绍vivado中仿真功能的使用

本文将详细介绍Vivado自带仿真器的主要特性

Vivado 软件提供了HDL编写中常用的示例

存储器是FPGA设计中的常用单元,对存储器的操作,最基础的就是读写操作

本文介绍了如何使用Verilog HDL实现ROM和RAM

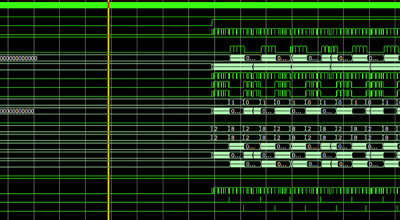

前面modelsim已经仿真成功了DDR3的初始化

有一个数据需要从A时钟域同步到B时钟域,数据位宽是512bit的

本文将介绍如何清理Vivado工程,并避免缺失必要的文件。