定制PYNQ的overlay

judy 在 周三, 01/09/2019 - 09:33 提交

一、用HLS生成一个定制IP(加速器)

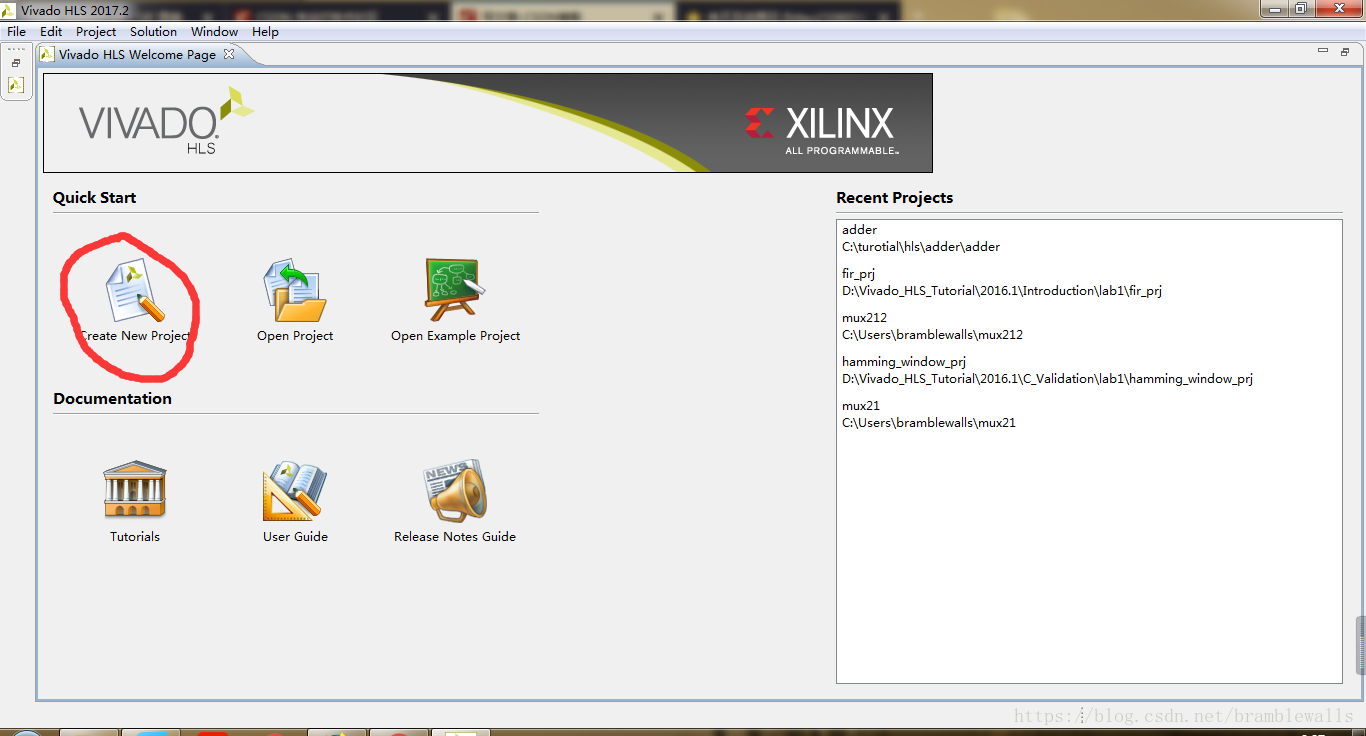

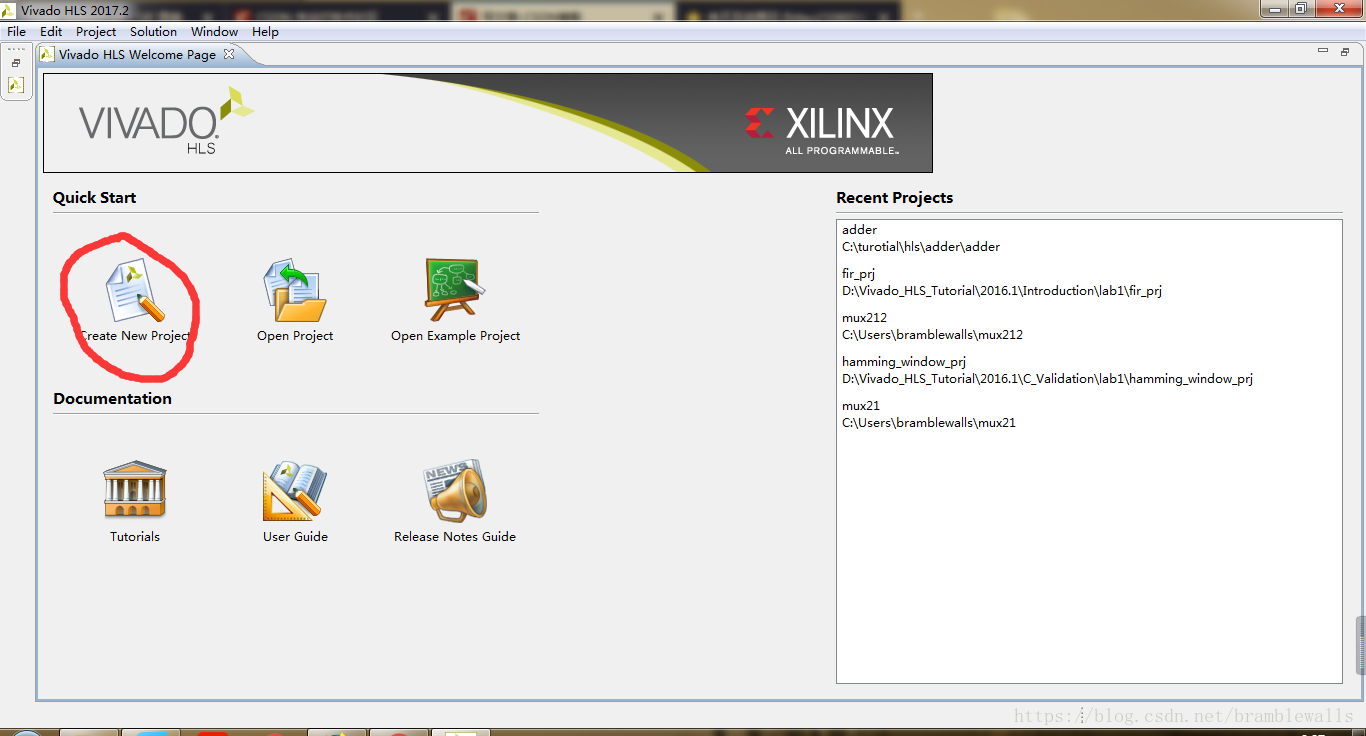

(1)首先打开vivado hls,本人的版本是2017.2,点击创建一个新工程。

(2)设置工程名和路径,顶层函数设置为add,创建一个新的C++程序,名字叫做adder.cpp,不用在testbench中添加文件。

选择板子的时候搜索xc7z020clg400-1,这是PYNQ的板子号,选择完成。

一、用HLS生成一个定制IP(加速器)

(1)首先打开vivado hls,本人的版本是2017.2,点击创建一个新工程。

(2)设置工程名和路径,顶层函数设置为add,创建一个新的C++程序,名字叫做adder.cpp,不用在testbench中添加文件。

选择板子的时候搜索xc7z020clg400-1,这是PYNQ的板子号,选择完成。

前面我们介绍了按键中断,其实我们稍作修改就可以用按键控制LED了。做个小实验,两个按键分别控制两个led亮灭。

板子:zc702。

硬件部分

添加zynq核:

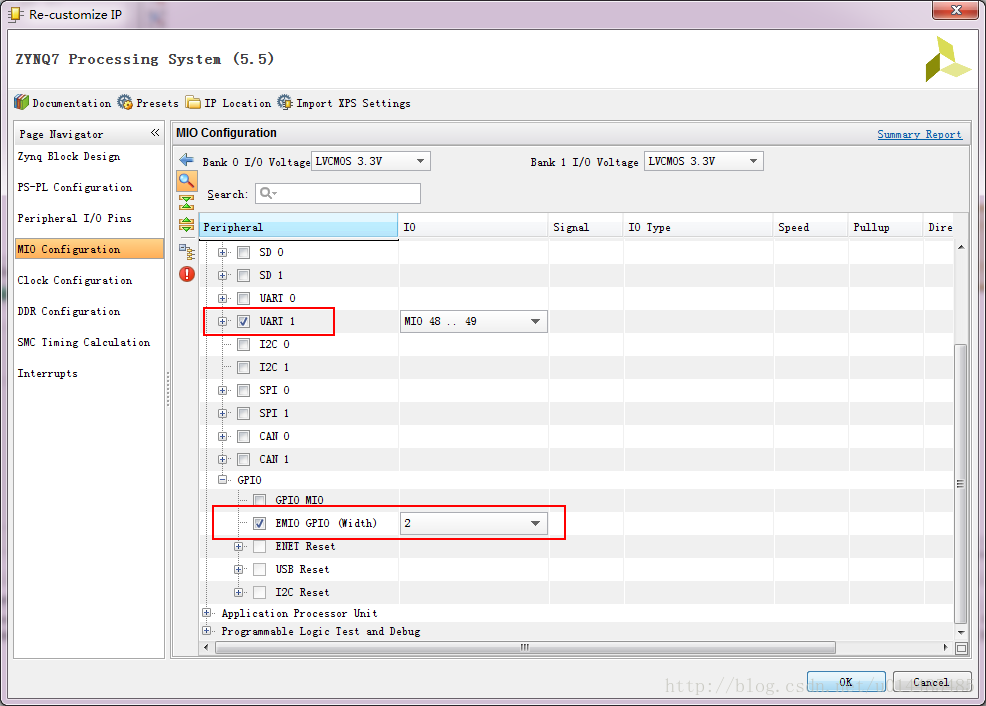

勾选串口用于打印信息,勾选EMIO,我们控制两个led,所以需要2bit

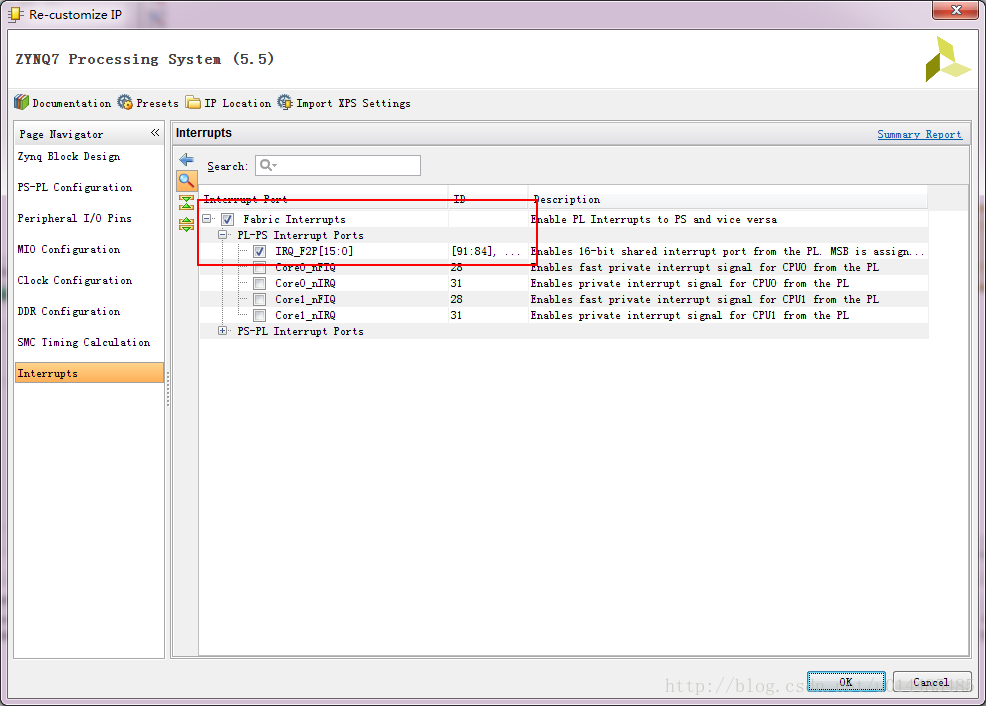

PL 到PS的中断勾选上:

PL时钟什么的都用不到,我们用的按键不需要时钟,EMIO属于PS。

再添加一个concat IP用于合并两路按键信号:

FPGA设计中经常用到一些控制逻辑,如有限状态机(FSM),如果用各种block搭建一个FSM比较麻烦。System Generator支持调用MATLAB代码,通常可以编写MATLAB代码来实现FSM等控制逻辑,通过MCode block调用到System Generator设计中。

1. 首先要在Ubuntu下安装Petalinux 2017.2

2. 设置Petalinux 环境变量

source /

3. 新建目录~/projets/fpga-drive-aximm-pcie

4. 把Windows下的Vivado工程复制到~/projets/fpga-drive-aximm-pcie下

5. 新建Petalinux工程

petalinux-create --type project --template zynq --name petalinux_prj

6. 切换到petalinux_prj目录

cd petalinux_prj/

7. 导入HDF

petalinux-config --get-hw-description ../fpga-drive-aximm-pcie-2017v2_hpc/Vivado/zc706_hpc_pcie/zc706_hpc_pcie.sdk/

随之弹出Linux System Configuration界面,不做任何更改,保存退出

Simulink中的仿真模型为连续时间系统,数据格式多种多样;而FPGA中为离散时间系统,数据必须用一定的位数进行量化。两者之间必须要进行从连续到离散的转换、数据格式的转换,否则无法进行正确的FPGA设计

文件系统用的Koheron提供的ubuntu16.04,将镜像文件解压后可以直接使用文件系统,具体使用命令的命令是fdisk 和mount

本文主要介绍一些常见的PCIe设计方案,针对PCIe接口的PCB设计。

FPGA挂载SATA SSD需要SATA IP,IP报价动辄十几W,开源的IP也有,但都是基于V6或者V5等老器件的。现在好了,NVME SSD大行其道,而且不需要IP,可以说为广大爱好者带来的福音

私有定时器属于PS部分,定时器可以帮我们计数、计时,有效的控制模块的时序。这一次实验我们认识定时器并使用定时器产生中断。

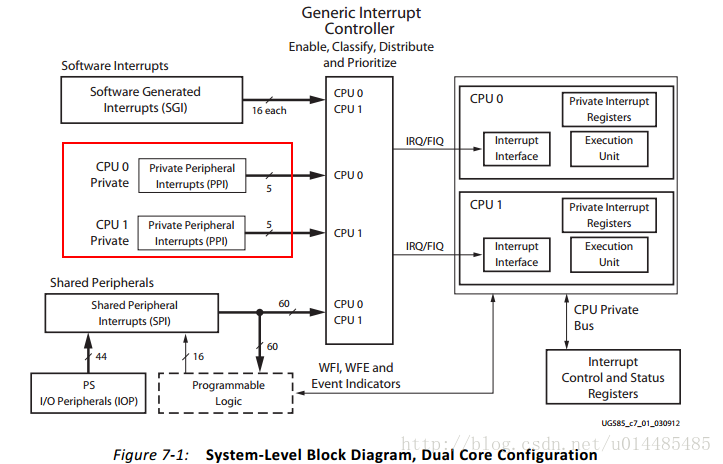

CPU的私有中断(PPI),5个:全局定时器, 私有看门狗定时器, 私有定时器以及来自 PL 的 FIQ/IRQ。

它们的触发类型都是固定不变的, 并且来自 PL 的快速中断信号 FIQ 和中断信号 IRQ 反向, 然后送到中断控制器因此尽管在ICDICFR1 寄存器内反映的他们是低电平触发,但是 PS-PL 接口中为高电平触发。

CPU的私有定时器:每个CPU都有自己的私有定时器:

私有定时器的工作频率是CPU的一半(频率仅供参考,主要看频率分配比率):

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用