FPGA实现串口升级及MultiBoot(三)FPGA启动加载方式

judy 在 周二, 09/10/2024 - 09:48 提交

上一篇中介绍了FPGA的启动步骤,如图0 所示,今天这篇文章就要在上一篇文章基础上进行分支细化,首先我们先了解FPGA 启动加载的几种方式

上一篇中介绍了FPGA的启动步骤,如图0 所示,今天这篇文章就要在上一篇文章基础上进行分支细化,首先我们先了解FPGA 启动加载的几种方式

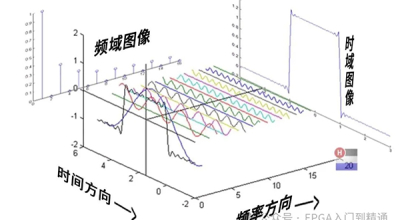

今天介绍一下并行 FIR 数字滤波器的原理以及实现。

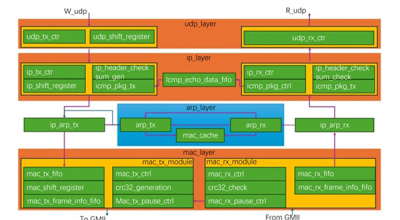

前面我们介绍了以太网的基本概念,及涉及的各层协议格式,接下来我们通过设计Verilog程序来实现以太网各个子层的功能

今天,就让我们一同深入这个充满魅力的数字信号处理基础——频域世界。

在写这篇文章时,我想了很多标题,但总感觉没有哪个能把文章的意思全都总结清楚的,所以我又起了副标题:断臂求生的Intel。

这个系列开篇肯定要先了解FPGA的启动流程,试想一下:我想实现MultiBoot,那么我应该在什么时候开始升级,升级失败后FPGA进行了哪些操作

数字电路中,小数可以用两种形式来表示:「定点数」和「浮点数」。浮点数的内容我们下篇文章再讲,本文只讲定点数。

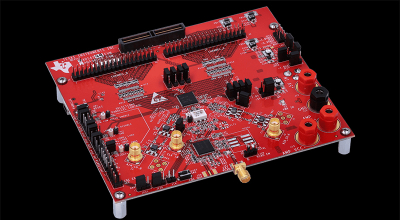

本文以TI的ADS4249(ADC)和DAC3482(DAC)之间的接口为例,介绍Altera FPGA与ADC/DAC之间的DDR LVDS接口设计以及时序约束详细设计。