Xilinx FPGA资源解析与使用系列——Transceiver(三)复位理解TXlane

judy 在 周四, 11/03/2022 - 09:22 提交

本文将结合ip example工程来理解transceiver的复位,通过学习记录,力求将其复位过程理解通透

本文将结合ip example工程来理解transceiver的复位,通过学习记录,力求将其复位过程理解通透

在平时工作中,经常会听到哪个FPGA或者某个芯片包含了几百万门,每次听到这种数字,很多FPGA工程师都会一愣一愣的

FPGA职业生涯可以怎么划分?是很多刚入门的FPGA新手们很陌生的一个话题。

Transceiver的环回功能对于调试和定位问题非常重要。环回有四种模式

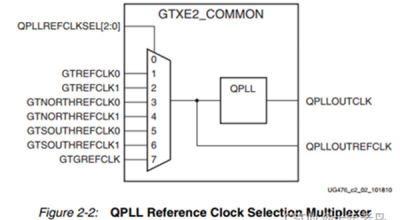

从IP核的时钟配置来学习transceiver的参考时钟架构细节

通过阅读IP手册可以知道,该IP支持的很多种浮点数计算,今天主要介绍最简单的加法操作

在使用vivado的过程中,如何添加设计文件?

书本中对于RAM的三种操作读优先级、写优先和保持使用等效的verilog来描述

在FPGA的设计中,不可避免的会用到FIFO和RAM这2个基本单元

本文将介绍将KV260上红色SOM换成K26 SOM后,如何从EMMC启动Linux。