Xilinx FPGA DDR3设计(一)DDR3基础扫盲

judy 在 周二, 06/07/2022 - 09:40 提交

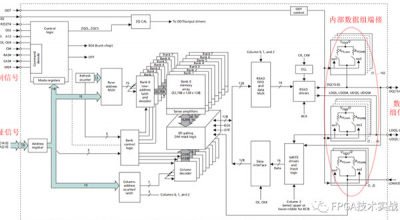

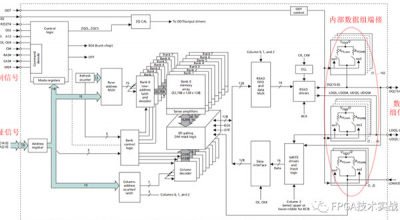

本文我们介绍下DDR3的基础知识,涉及DDR3管脚信号、容量计算、重要参数介绍内容

本文我们介绍下DDR3的基础知识,涉及DDR3管脚信号、容量计算、重要参数介绍内容

本文就针对IP设计中注意事项、有用策略及FPGA原型设计等进行简要说明。

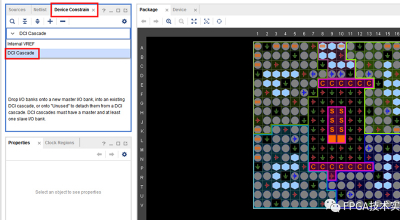

Vivado®Design Suite提供了几种可能影响I/O和时钟规划的器件规划功能。例如,FPGA配置方案、约束、配置电压方式都会影响I/O和时钟规划。

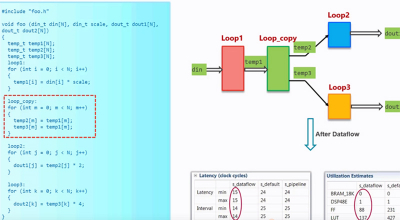

本文通过例子中来解释for循环中的基本概念

本文以JTAG to AXI Master调试AXI BRAM 控制器举例说明 JTAG 到 AXI Master 的使用方法。

如何获取Xilinx FPGA的Device DNA呢,下面我从JTAG和调用源语两个方法说明,并开放核心代码供大家参考。

本文主要介绍时钟及I/O规划的各个阶段及流程要点。

采用任意精度数据类型,可以在获得相同精度的运算条件下,运算速度更快且使用更少的资源。

本文我们介绍FPGA外设DDR2/DDR3硬件设计相关内容,包括PCB板层数估计,信号端接、信号完整性及时序考虑等问题。

本文我们通过一个具体的实例,演示HLS设计流程。