FPGA的IO到底是怎么命名的?

judy 在 周四, 10/15/2020 - 09:18 提交

今天想和大家一起聊聊FPGA的IO。先说说我当年入门的经历吧。国内的大学有FPGA开发条件的实验室并不太多,当年大学的那帮同学有的做ARM,有的做linux,很少有人做FPGA,当时学FPGA仅仅是由于非常渴望的好奇心。所以,在淘宝买了一块开发板,就开始了自己的FPGA之路。

今天想和大家一起聊聊FPGA的IO。先说说我当年入门的经历吧。国内的大学有FPGA开发条件的实验室并不太多,当年大学的那帮同学有的做ARM,有的做linux,很少有人做FPGA,当时学FPGA仅仅是由于非常渴望的好奇心。所以,在淘宝买了一块开发板,就开始了自己的FPGA之路。

对于使用AXI总线,最开始肯定要了解顶层接口定义,这样才能针对顶层接口进行调用和例化,打开axi_lite_v1_0.v文件,第一段就是顶层的接口定义:

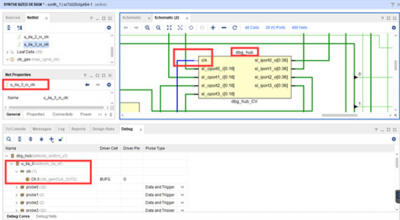

要看到AXI-Lite的源码,我们先要自定义一个AXI-Lite的IP,新建工程之后,选择,菜单栏->Tools->Creat and Package IP

新手必看:Vivado工程升级及板级信号调试

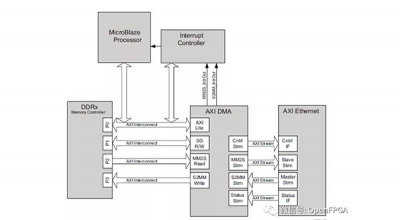

基于AXI的DMA对内部寄存器的读写有着相同的方式。在普通传输模式下,DMA内部的寄存器都是由处理器通过AXI-Lite总线进行读写的;但基于AXI总线的三种DMA,都增加了S/G传输模式,它卸载了处理器对寄存器的读写,通过独立的S/G读写通道对存储着命令描述符的内存进行访问读取、处理描述符,然后更新描述符写入内存。

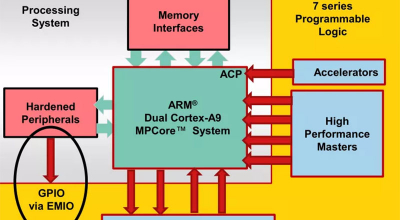

复位系统包括由硬件,看门狗定时器,JTAG控制器和软件产生的复位。Zynq-7000 SoC器件中的每个模块和系统都包含一个由复位系统驱动的复位。硬件复位由上电复位信号(PS_POR_B)和系统复位信号(PS_SRST_B)驱动。

ZYNQ架构:双核ARM Cortex-A9 处理器:ARM Cortex-A9 是一个应用级的处理器,能运行完整的像Linux 这样的操作系统,传统的现场可编程门阵列(Field Programmable Gate Array,FPGA)逻辑部件:基于Xilinx 7 系列的FPGA 架构

几个常用的 AXI 接口 IP 的功能(上面已经提到):

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换

AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<----->AXI-Stream 的转换

在ZYNQ的体系结构中定时器太丰富了,而大量的教程中基本就只玩了私有定时器,可以中断就OK了。其实在ZYNQ中定时器资源很丰富,每个CPU有自己的私有定时器和看门狗,有一个所有CPU共享的全局定时器和看门狗,两个三路定时器还有AXI_TIMER的IP可用,不过好像很少有博客把这些测试完。

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI-Lite或AXI4转接。PS与PL之间的物理接口有9个,包括4个AXI-GP接口和4个AXI-HP接口、1个AXI-ACP接口