System Generator从入门到放弃(二)——Digital Filter

judy 在 周四, 12/27/2018 - 16:34 提交

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用

Zynq系列FPGA分为PS部分和PL部分。

PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分。

PS: 处理系统 (Processing System) , 就是与FPGA无关的ARM的SOC的部分,实质是直接操作arm9内核的处理器。

这次先是最简单地在PL部分编写一个流水灯实验的代码。

使用的开发环境是vivado 2016.4。

1、新建工程,Create New Project。

2、next。

3、选择工程目录,和输入工程名字。

PS和PL之间的交互,怎么都逃不过中断,稍微大型的数字系统,PS和PL之间配合使用就需要中断作为桥梁。本文通过按键发起中断请求尝试学习PL请求中断的处理机制。

环境准备

首先肯定是要下载xilinx-2011.09-50-arm-xilinx-linux-gnueabi.bin文件,这是官方提供的linux下交叉编译链安装文件,下载地址为:https://pan.baidu.com/s/1eSP85nO 。

安装交叉编译环境工作:

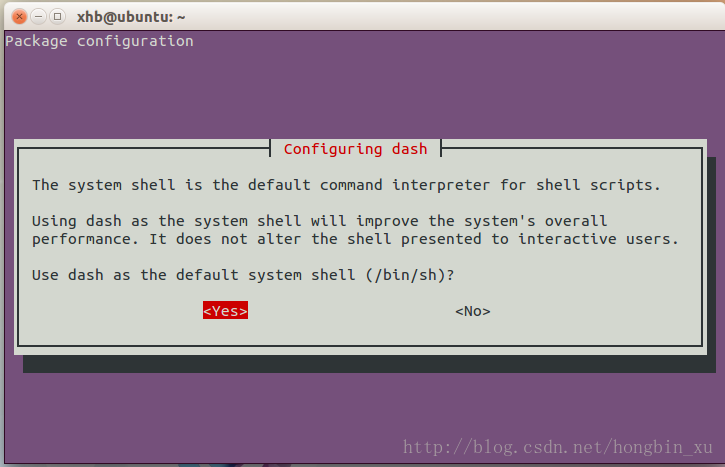

1、由于安装文件只能在bash下运行,所以要将dash改为bash,输入以下指令:

sudo dpkg-reconfigure -plow dash

选择No,切换到bash。

2、建立一个文件夹作为安装路径;

我的指定的安装目录为:/opt/cross_compiler

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用

Block RAM是PL部分的存储器阵列,为了与DRAM(分布式RAM)区分开,所以叫块RAM。ZYNQ的每一个BRAM 36KB,7020的BRAM有140个(4.9M),7030有265个(9.3M),7045有545个(19.2M)。每一个BRAM都有两个共享数据的独立端口,当然是可以配置的,可用于片内数据缓存、FIFO缓冲

在写资源管理器的时候,一般会用到处理close()来进行一些收尾工作,比如释放内存等等,查看QNX代码resmgr_io_funcs_t结构体对close()的处理有两个相关函数

程序的格式框架

下面是一段温度转换的代码示例:

#TempConvert.py

TempStr = input("请输入带有符号的温度值:")

if TempStr[-1] in['F','f']:

C = (eval(TempStr[0:-1]) - 32)/1.8

print("转换后的温度是{:.2f}F".format(F))

elif TempStr[-1] in['C','c']:

F = 1.8*eval(TempStr[0:-1]) + 32

print("转换后的温度是{:.2f}F".format(F))

else:

print("输入格式错误")

代码高亮是变成的色彩辅助体系,不是语法要求,可以检查基本语法拼写错误

首先,需要的肯定是Ubuntu操作系统。可以在自己的电脑上安装物理机,也可以是虚拟机下运行的。我的是在Vmware下运行的Ubuntu14.04 32位操作系统。由于zedboard上的Linux操作系统跑的是32位的,为了省去麻烦,我没有安装64位的

前面我们介绍过EMIO,但是不详细。MIO是PS的IO接口,这个M代表的是Multiuse,也就是多用途,在下图中我们可以看到54个MIO连接这么多东西,必须得复用,所以当我们开发的时候需要的功能配置上,不需要的去掉,防止IO口被占用