Vivado使用技巧(33):时序异常

judy 在 周一, 04/15/2019 - 10:51 提交

Vivado不支持即时分析有矛盾的时序异常,需要运行report_exceptions进行完整的分析,报告所有时序异常。多周期路径的情况有很多,比较复杂,单独放在第35篇中讲述。本文介绍其余三种时序异常的相关知识。

Vivado不支持即时分析有矛盾的时序异常,需要运行report_exceptions进行完整的分析,报告所有时序异常。多周期路径的情况有很多,比较复杂,单独放在第35篇中讲述。本文介绍其余三种时序异常的相关知识。

作者:liuyayong

1、实验方案

图1 实验方案系统框图

2、具体步骤

2.1、vivado工程建立

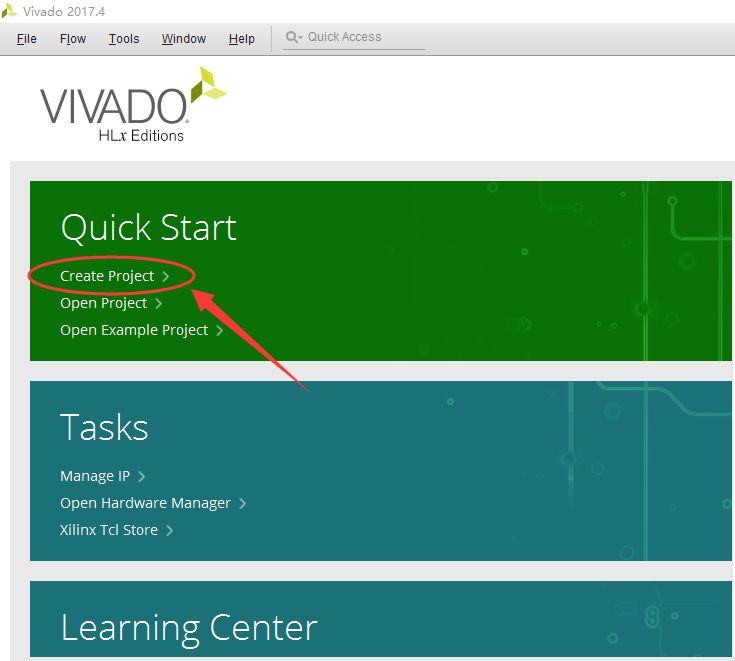

①打开vivado集成开发环境,点击“Create Project”,如下图所示。

②点击“Next”,如下图所示。

上一篇简单解释了Zynq配置的相关概念,本文将对Zynq-7000的软件开发进行简单介绍。如果设计者已经对ARM的开发方法很熟悉,上手Zynq的软件开发也会更快,相关概念理解起来也更快。

上电自复位对FPGA的稳定性及其重要,因为对于某些设计,上电之后需要进行一些状态寄存器的初始化,或者系统自己初始化都需要一个复位信号。在这里我就介绍一个比较好用的方法,大家一起学习一下

上一篇讲述了对时钟的约束方法,时钟不仅对设计很重要,约束情况也很多、很复杂,需要一定的经验。本文将讲述另一种重要的约束:I/O延迟,但与时钟约束相比就简单的多,本文篇幅也相对较少。

本文档系列是我在实践将简单的神经网络LeNet-5实现到Xilinx 的zynq-7z035的FPGA上遇到的问题和解决方法。本文档重点探讨vivado软件的使用。

上篇中介绍了Xilinx FPGA嵌入式开发的基本概念和软件特性,并以Hello World为例给出了一个操作流程,熟悉该流程相当重要。上一篇中只是简单说明了每一步应该执行哪些操作,本文将详细介绍每一步的具体含义和涉及到的相关概念。

在做FPGA的开发过程中经常会使用到移位寄存器,一般我们使用移位寄存器的目的都是为了将某个信号进行打拍,使得时序符合我们的需求。最常见的一种打拍方法就是在process过程语句中对信号进行移位。但是这里我给大家介绍一下SRL6E

本系列将讲述如何使用Vivado完成基于Zynq平台的嵌入式系统设计。一个完整的嵌入式系统设计要考虑硬件、软件、FPGA设计三个部分。Xilinx为了尽量简化设计流程,提供如下两个主要设计工具

背景:zynqNet运用HLS来实现相应的IPcore。相关HLS过程的信息会打印到console之中。目的:读懂HLS对IPcore代码的HLS过程,具体硬件如何实现。将报告信息存下来用于参考。