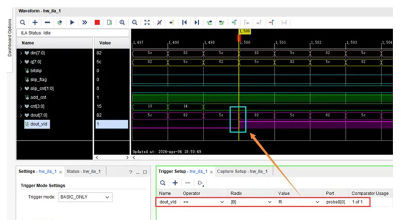

输入信号绕过ilogic布线冲突引发的问题(idelaye2使用)

judy 在 周四, 12/19/2024 - 11:35 提交

从最初学FPGA到现在,遇到过太多bug,但都没有写过博客记录,因为多数问题都比较简单且网上有比较好的答案

从最初学FPGA到现在,遇到过太多bug,但都没有写过博客记录,因为多数问题都比较简单且网上有比较好的答案

FPGA并没有像软件那样用已有的cache,FPGA的HLS编译器会在FPGA中创建一个快速的memory architecture以最好的适应算法中的数据样式(data layout)

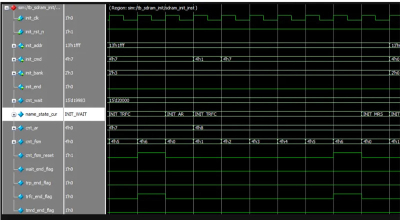

最近在网上看并没有用户对ISERDESE2的使用讲解的很清晰,所以本文就通过手册、仿真和ILA去讲解一下这个原语的使用方式,希望对大家的使用有所帮助。

SDRAM 的初始化是芯片上电后必须进行的一项操作,只有进行了初始化操作的 SDRAM 芯片才可被正常使用

本文将详细介绍FPGA分频器的设计方法,并附上Verilog代码示例,以供参考

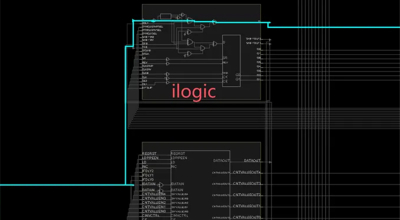

7系列IO模块相关的结构如图1所示,前文对IOB、IDELAYE2、ILOGIC、OLOGIC进行了讲解,还剩下ISERDESE2、OSERDESE2、ODELAYE2原语

本次项目展示了如何创建 CLI 来控制机械臂的 PWM 驱动器。还创建了一个详细的 Python 应用程序,该应用程序与 AMD MicroBlaze™ V 配合使用

以下是您需要了解的有关这些尖端半导体的所有信息,随着全球对人工智能的狂热,它们的需求也飙升。

SDRAM具有空间存储量大、读写速度快、价格相对便宜等优点。然而由于SDRAM内部利用电容来存储数据,为保证数据不丢失,需要持续对各存储电容进行刷新操作