Zedboard学习(八):zedboard移植opencv

judy 在 周四, 01/31/2019 - 10:33 提交

首先要说明的是,往zedboard上移植opencv跟我们平时在pc上安装opencv的过程不同。毕竟zedboard是嵌入式平台很多东西都要删减,而且zedboard官方移植的linux不带图形界面,我们要自己在命令行下配置环境

首先要说明的是,往zedboard上移植opencv跟我们平时在pc上安装opencv的过程不同。毕竟zedboard是嵌入式平台很多东西都要删减,而且zedboard官方移植的linux不带图形界面,我们要自己在命令行下配置环境

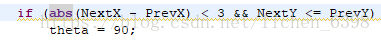

在viado SDK的程序开发中会出现以下的问题

出现问题的原因可能是

没有添加对应的头文件

解决办法:添加对应的头文件 如上图:添加#include”stdlib.h”

没有添加库函数

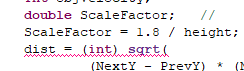

解决的方法是:

点击工程文件,右键,选择Properties

如下图:

选择 C/C++ Build 下的Setting 选择:Libraries 添加m文件 因为abs()位于math.h函数里

背景:ZynqNet能在xilinx的FPGA上实现deep compression。

目的:读懂zynqNet的代码和论文。

一、网络所需的运算与存储

1.1 运算操作:

1.2 Memory requirements:

1.3 需求分析:

在介绍Gateway In block时谈到了System Generator中的数据类型,及不同的量化和溢出方式。本文将以两个简单的设计实例,更直观地说明不同的量化和溢出方式有什么区别。

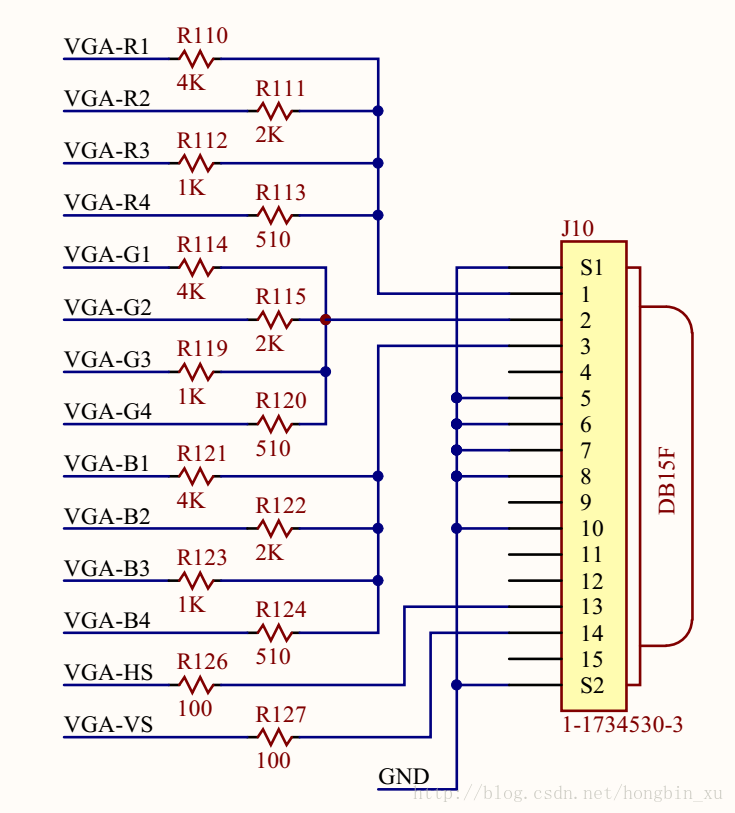

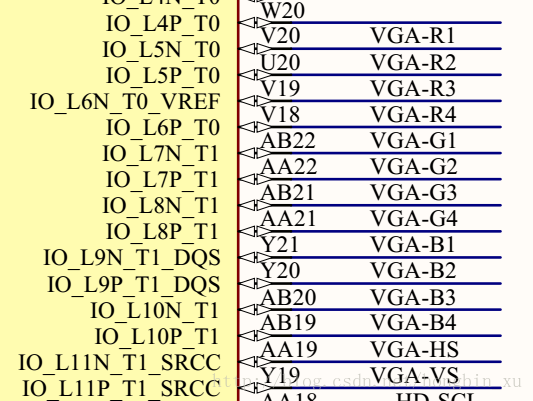

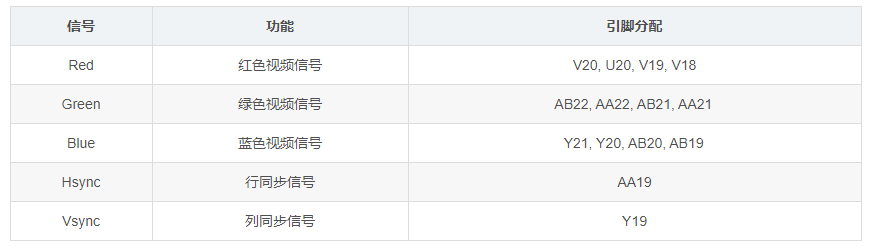

VGA硬件接口

到zedboard官方给出的原理图中查看:

RGB信号,各四位;这里的设计是使用了电阻分压模拟了DAC芯片实现了4X4X4的RGB信号,如果要更好的显示效果还是建议使用专门的DAC。

上面给出了所有的引脚分配。

VGA时序分析

zynq 的内嵌了 XADC,可以用来采集电压;

Temp:芯片温度

VCCINT: 内部PL核心电压

VCCAUX: 辅助PL电压

VCCBram: PL BRAM电压

VCCPInt: PS内部核心电压

VCCPAux: PS辅助电压

VCCDDR: DDR RAM的工作电压

VREFP: XADC正参考电压

VREFN: XADC负参考电压

1、新建工程,添加block design。添加zynq7 processor和xadc模块。

2、Run Block Automation后会自动配置zynq7处理器;Run Connection Automation 会自动将模块进行连接,将xadc模块挂载在axi总线下,这样xadc的相关寄存器会映射到处理器的内存(DDR)上。自动添加的两个模块,一个用于管理全局复位,一个用于同步axi总线。

ZCU102实时YUV码流输出方案:将摄像头采集的数据,输出YUV的码流数据!功能:将实时YUV码流在ZCU102BSP上编码H265,通过RTP传输协议将H265视频数据打包发送到客服端,客服端上设置H265相关参数(IP、端口号、时钟频率等)在sdp文件中,使用VLC播放实时的H265码流

FPGA(现场可编程门阵列)是半导体器件,通过设计实现具有可编程互连的逻辑块阵列。与“硬化”设备(即CPU / GPU)不同,FPGA可以编程为实现用户所需的特定硬件设计。在设计硬件系统之后,必须使用二进制文件对FPGA进行编程。此过程通常称为配置。此外,在具有固定功能和动态功能的用例中,可以部分地重新配置FPGA

前面的中断学习中我们学了按键,GPIO,Timer,是时候把它们整合到一起了。今天我们混合使用PS/PL部分的资源,建立一个比较大的系统

Zynq7000 系列芯片有 54 个 MIO(multiuse I/O), 它们分配在 GPIO 的 Bank0 和Bank1 隶属于 PS 部分, 这些 IO 与 PS 直接相连。 不需要添加引脚约束, MIO 信号对 PL部分是透明的。 所以对 MIO 的操作可以看作是纯PS 的操作