SoC中IP化设计的考虑因素总结

judy 在 周一, 06/06/2022 - 09:35 提交

本文就针对IP设计中注意事项、有用策略及FPGA原型设计等进行简要说明。

本文就针对IP设计中注意事项、有用策略及FPGA原型设计等进行简要说明。

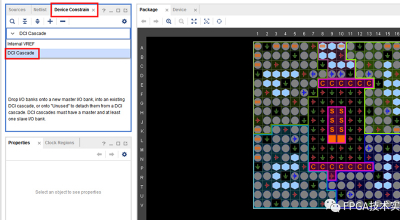

Vivado®Design Suite提供了几种可能影响I/O和时钟规划的器件规划功能。例如,FPGA配置方案、约束、配置电压方式都会影响I/O和时钟规划。

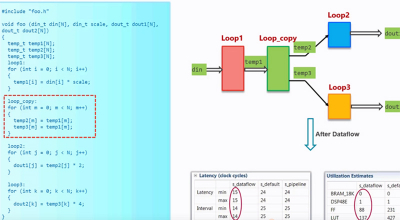

本文通过例子中来解释for循环中的基本概念

本文以JTAG to AXI Master调试AXI BRAM 控制器举例说明 JTAG 到 AXI Master 的使用方法。

如何获取Xilinx FPGA的Device DNA呢,下面我从JTAG和调用源语两个方法说明,并开放核心代码供大家参考。

本文主要介绍时钟及I/O规划的各个阶段及流程要点。

采用任意精度数据类型,可以在获得相同精度的运算条件下,运算速度更快且使用更少的资源。

本文我们介绍FPGA外设DDR2/DDR3硬件设计相关内容,包括PCB板层数估计,信号端接、信号完整性及时序考虑等问题。

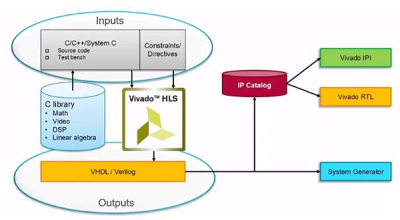

本文我们通过一个具体的实例,演示HLS设计流程。

传统的FPGA RTL设计流程主要是采用VHDL、VerilogHDL或System Verilog进行工程的开发,同时也是通过硬件描述语言来编写测试案例对开发的工程进行仿真验证