Vitis DPU加速设计流程总结

judy 在 周二, 08/31/2021 - 17:23 提交

本文对vitis设计流程进行总结

本文对vitis设计流程进行总结

在Vitis下运行DNNDK例程时,(例程地址https://github.com/Xilinx/Vitis-In-Depth-Tutorial/blob/2020.1/Vitis_Plat...)运行到编译时,(20 Right click the hello_dpu project folder and select Build Project)一直出如下错误

Vitis统一软件平台将Xilinx各种软件统一,即支持Vitis嵌入式软件开发流程,又支持Vitis应用软件加速开发流程。本文介绍Vitis嵌入式软件中的linux应用程序开发流程。

PYNQ结合了Zynq与Python的优势,是机器学习/人工智能、边缘计算、大数据处理等算法加速的优秀平台。PYNQ这个名字来自于Python productivity for Zynq,PYNQ使用Python语言简化了Zynq应用程序开发过程。

Vitis官方文档主要有两个ug1400和ug1393 ,ug1400主要针对嵌入式软件设计,ug1393针对应用加速设计。本文结合以上两个文档,主要针对Zynq®-7000 SoC,和Zynq® UltraScale+™ MPSoCs应用加速开发流程进行简要介绍。

布局规划是为设计增加布局布线约束的过程。一个大型高速设计的布局规划是实现时序收敛的关键。好的布局规划可以大大提高设计性能,并确保设计结果的质量。差的布局规划具有相反的效果,使其无法满足时序约束,并导致设计结果与预期不符

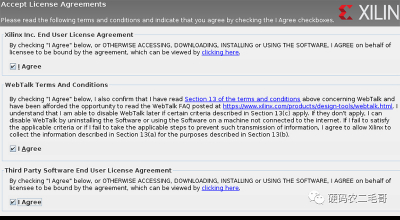

Xilinx工具最新版本已经更新到2020.2,我之所以安装2020.1主要是因为PYNQ最新版本V2.6支持2020.1,今年会做一些PYNQ相关的开发。

在文章中如何将zcu106例程移植到自定义单板,描述了如何在自定义单板平台构建硬件平台、软件系统添加配方,运行zcu106例程。实现过程很复杂。zcu106单板的bsp不能直接用在习惯单板上呢?下面是我做的一些试点,大家可以参考。

在zcu106开箱即用vcu示例中用到了USB摄像头,本节介绍如何对摄像头输出图像进行编解码。

软硬件系统构建好之后,VCU可以正常工作了。可以在VCU软件堆栈的不同层次上对VCU进行编解码,下面介绍一下使用VCU控制软件如何进行编解码。