CMOS和TTL与非门多余输入端处理方法【门电路相关问题】

judy 在 周四, 05/06/2021 - 09:45 提交

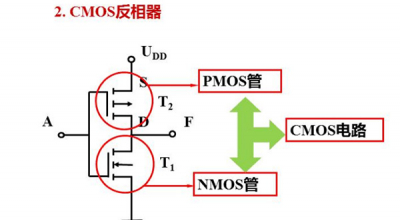

CMOS与非门,只要有一个输入端为低电平,与运算后均为低电平,输出为高电平,影响了输出结果,若接地或悬空会使输出始终为 1。CMOS与门、与非门:多余端通过限流电阻(500Ω)接电源;CMOS或门、或非门:多余端通过限流电阻(500Ω)接地;

CMOS与非门,只要有一个输入端为低电平,与运算后均为低电平,输出为高电平,影响了输出结果,若接地或悬空会使输出始终为 1。CMOS与门、与非门:多余端通过限流电阻(500Ω)接电源;CMOS或门、或非门:多余端通过限流电阻(500Ω)接地;

选择了xilinx zynq7z035ffg676这个型号的板子,是因为需要做定位通信的项目。AD9361+ZYNQ 的组合,因为需要自己一个人做PL和PS端的工作,这两部分的很多细节我都不了解,于是我向老板的一个专门做这块的朋友请教了我的一些问题,下面继续来整理一下。

依稀记得,当我第一次接触ZYNQ的时候,是在一个从零开始的项目中,可以说是需求都没确定,只是需要FPGA与ARM结合的平台,在迷茫的选择中,我选择了xilinx zynq7z035ffg676这个型号的板子

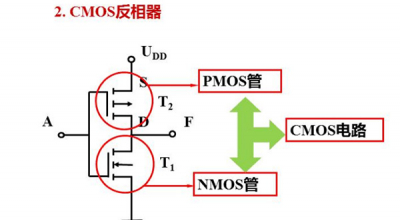

两大优化方向:面积优化、速度优化,相互制约。

XILINX FPGA 芯片整体架构如下所示,整个芯片是以BANK进行划分的,不同的工艺、器件速度和对应的时钟具有不同的BANK数量(下面截图是以K7325tffg676为例):左边的BANK都是HR BANK,右侧的最下面三个是HP BANK,最上面的四个BANK是transceiver

虽然很多FPGA工程师都是写代码,但是作为硬件编程工程师,如果不熟悉FPGA的底层资源和架构,是很难写出高质量的代码——至少很难写出复杂逻辑的高质量代码,也很难站在系统的层面去考虑芯片的选型等问题。那熟悉FPGA架构,首先最主要的一点,我们先来了解FPGA的IO

Xilinx FPGA都有一个独特的 ID ,也就是 Device DNA ,这个 ID 相当于我们的身份证,在 FPGA 芯片生产的时候就已经固定在芯片的 eFuse 寄存器中,具有不可修改的属性。在xilinx 7series 和 7series 以前,ID 都是 57bit 的,但是在 Xilinx 的 Ultraslace 架构下是 96bit 。

DQ0-7 八根线必须连到同一T块(也称为字节组)上,一旦分在一起,这个字节组就不能放地址线和控制线了,只能放数据线。 每组数据线对应的DQS必须连到N6,N7上,也就是QBC或者是DBC上

今天带来第六篇,介绍配置Vitis IDE和项目进出口。

.mif 和 .coe 是 FPGA 设计中常用的存储文件,用于 ROM、RAM 等存储器数据的加载,常见的还用在 DDS 信号发生器和 FIR 滤波器的设计中。 .txt 文件主要用于 Matlab 和 FPGA 的联合仿真,比如在滤波器的设计中,可以使用 Matlab 先把加噪声的信号写入到 .txt 文件,然后 FPGA 仿真中在 Testbench 中读取该信号源的数据