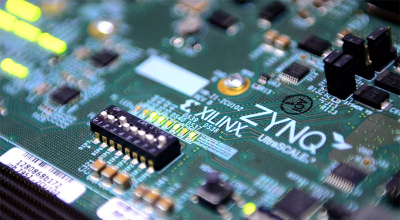

【Vivado那些事】FPGA配置失败,无法启动怎么办

judy 在 周一, 02/01/2021 - 09:42 提交

都知道FPGA的启动方式有很多种,比如JTAG、SPI,BPI,SeletMAP,Serial等等吧,又分为主从即Master和Slave(时钟由FPGA的管脚发出,专用的CCLK信号为主,否则为从,有的配置有辅助时钟EMCCLK,它由外部的晶振提供,从FPGA的EMCCLK输入,经过专用的逻辑,再从CCLK管脚输出给想用的器件,),那么问题来了,配置失败怎么办呢??????????????