几种应用DMA的典型应用

judy 在 周二, 09/29/2020 - 09:33 提交

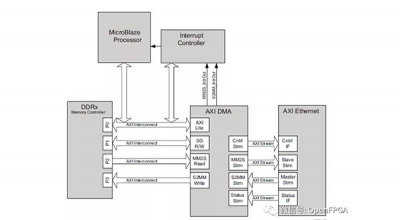

基于AXI的DMA对内部寄存器的读写有着相同的方式。在普通传输模式下,DMA内部的寄存器都是由处理器通过AXI-Lite总线进行读写的;但基于AXI总线的三种DMA,都增加了S/G传输模式,它卸载了处理器对寄存器的读写,通过独立的S/G读写通道对存储着命令描述符的内存进行访问读取、处理描述符,然后更新描述符写入内存。

基于AXI的DMA对内部寄存器的读写有着相同的方式。在普通传输模式下,DMA内部的寄存器都是由处理器通过AXI-Lite总线进行读写的;但基于AXI总线的三种DMA,都增加了S/G传输模式,它卸载了处理器对寄存器的读写,通过独立的S/G读写通道对存储着命令描述符的内存进行访问读取、处理描述符,然后更新描述符写入内存。

复位系统包括由硬件,看门狗定时器,JTAG控制器和软件产生的复位。Zynq-7000 SoC器件中的每个模块和系统都包含一个由复位系统驱动的复位。硬件复位由上电复位信号(PS_POR_B)和系统复位信号(PS_SRST_B)驱动。

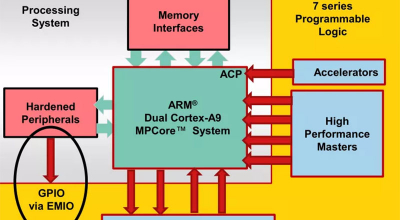

ZYNQ架构:双核ARM Cortex-A9 处理器:ARM Cortex-A9 是一个应用级的处理器,能运行完整的像Linux 这样的操作系统,传统的现场可编程门阵列(Field Programmable Gate Array,FPGA)逻辑部件:基于Xilinx 7 系列的FPGA 架构

几个常用的 AXI 接口 IP 的功能(上面已经提到):

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换

AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<----->AXI-Stream 的转换

在ZYNQ的体系结构中定时器太丰富了,而大量的教程中基本就只玩了私有定时器,可以中断就OK了。其实在ZYNQ中定时器资源很丰富,每个CPU有自己的私有定时器和看门狗,有一个所有CPU共享的全局定时器和看门狗,两个三路定时器还有AXI_TIMER的IP可用,不过好像很少有博客把这些测试完。

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI-Lite或AXI4转接。PS与PL之间的物理接口有9个,包括4个AXI-GP接口和4个AXI-HP接口、1个AXI-ACP接口

这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

这里主要介绍三种跨时钟域处理的方法,这三种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这三招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来

glitch:毛刺,glitch-free clock switching circuit:无毛刺时钟切换电路,今天讨论的主题就是如何实现时钟的无毛刺切换,本文将从有毛刺的时钟切换电路、无毛刺的源同步时钟切换电路、无毛刺的异步时钟切换电路三方面展开

AXI4协议基于猝发式传输机制。在地址通道上,每个交易有地址和控制信息,这些信息描述了需要传输的数据性质。主从设备间的数据传输有两种情况,一种是主设备经过写通道向从设备写数据(简称写交易),另一种是主设备经过读通道从从设备那里读取数据(简称读交易)