PCIe系列第三讲、事务层通用 TLP 头结构分析

judy 在 周二, 07/07/2020 - 09:26 提交

上一讲说道:“一个完整的TLP由1个或多个TLP Prefix、TLP头、Data Payload和TLP Digest构成”,那么本讲将就谈一谈TLP的头,具体几种事务(存储器读写、配置读写、IO读写、原子操作、消息报文)后面一一分析。

上一讲说道:“一个完整的TLP由1个或多个TLP Prefix、TLP头、Data Payload和TLP Digest构成”,那么本讲将就谈一谈TLP的头,具体几种事务(存储器读写、配置读写、IO读写、原子操作、消息报文)后面一一分析。

现在的FPGA设计,规模巨大而且功能复杂,因此设计的每一个部分都从头开始是不切实际的。一种解决的办法是:对于较为通用的部分可以重用现有的功能模块,而把主要的时间和资源用在设计中的那些全新的、独特的部分。这就像是你在开发应用程序的时候就不用直接去写驱动物理硬件的代码

之前有分享过《modelsim se 2019.2安装教程》及《vivado2018 中使用modelsim联合仿真》,今天就带来Vivado与Modesim联合仿真的一些注意点

在FPGA中我们写的最多的逻辑是什么?相信对大部分朋友来说应该都是计数器,从最初板卡的测试时我们会闪烁LED,到复杂的AXI总线中产生地址或者last等信号,都会用到计数器,使用计数器那必然会用到进位链。

LFSR:线性反馈移位寄存器(linear feedback shift register, LFSR)是指给定前一状态的输出,将该输出的线性函数再用作输入的移位寄存器。异或运算是最常见的单比特线性函数:对寄存器的某些位进行异或操作后作为输入,再对寄存器中的各比特进行整体移位。

PCIe协议定义了三层结构,分别是:物理层、数据链路层、事务层,每个层次按照协议中规定的内容,完成相应的数据处理功能,各层都分为发送和接收两功能块。在Xilinx芯片内部集成有PCIe硬核端点模块,能够自动完成数据链路层和物理层的数据处理

PCIe2.0规范于2007年1月5日推出,将PCIe1.0 2.5GT/s的传输速率提高了一倍,每个通道的吞吐率从250MB/s上升到500MB/s,因此2通道的PCIe可支持高达1GB的总吞吐量。

Xilinx 7系列FPGA内置了一个模数转换模块,称为XADC。XADC内部集成了两个最高1MHz采样率,1Vpp的ADC模块,可以采集FPGA外部输入的模拟信号并转为数字信号。XADC不需要外接任何输入信号,就可以测量FPGA内部的温度,VCCINT,VCCBRAM,VCCAUX电压。

AXI4 从站接口将 AXI4 事务映射到 UI,以向内存控制器提供行业标准总线协议接口。UI 块向用户提供 FPGA 逻辑块。它通过呈现平面地址空间和缓冲读写数据来提供对本机接口的简单替代。

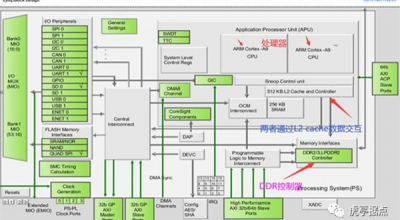

在ZYNQ的PS侧存在Cache,CPU与DDR之间通过Cache进行交互,数据暂存在Data cache中,在处理器对DDR进行写数据操作时,如果不将数据通过Cache送入DDR,DDR中的数据不会变化。在进行DMA操作时,如果没有对Cache进行适当的操作,可能导致以下两种错误