FPGA项目开发之同步信号和亚稳态

judy 在 周三, 10/19/2022 - 10:08 提交

让我们从触发器开始,所有触发器都有一个围绕活动时钟沿的建立(setup time)和保持窗口(hold time)

让我们从触发器开始,所有触发器都有一个围绕活动时钟沿的建立(setup time)和保持窗口(hold time)

将管脚输入的第一个触发器使用ILOGIC来实现有助于每次编译过程中时序的确定性。

本文继续介绍Xilinx 7系列FPGA SelcetIO电平标准及相关端接匹配电路。

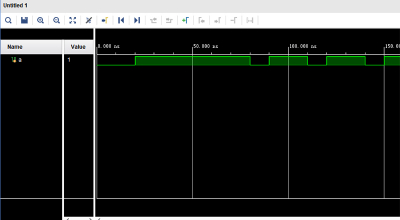

系统任务$finish的作用是退出仿真器,结束仿真过程

应用笔记简要描述Xilinx Zynq 系列器件XADC的相关资源及若干种应用

学会如何根据手册配置 MIG IP 核中的参数。

保持时间是对触发器而言,以能够稳定准确的锁存或者触发为目的

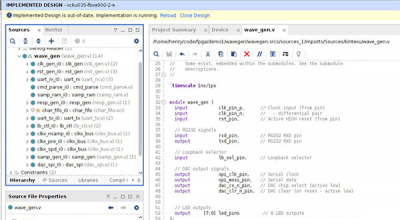

vivado有project模式和non-project模式,project模式就是我们常用的方式

这篇文章讲了地址映射的实现方法以及需注意事项。