从FPGA说起的深度学习(五)

judy 在 周五, 03/10/2023 - 09:37 提交

在本文中,我们将结合这些层来创建一个完整的推理函数

在本文中,我们将结合这些层来创建一个完整的推理函数

FPGA的实现过程可以对综合后生成的网表进行逻辑综合优化、以及布局、布线方面的优化

这篇文章将讨论如何在 verilog 中使用不同的运算符,这些运算符提供了一种在 verilog 设计中处理数字数据的方法

通过本文的阅读,您将了解如何抢先一步,使用FPGA来加速深度学习计算

FPGA设计中常见的一个场景就是逻辑需要查存放在外部DDR中的表项,如果查外部DDR中的表项是性能瓶颈点怎么办呢?

此 API 函数为请求的 RF-ADC 设置抽取因子,并根据抽取因子更新 FIFO 写入宽度

本文借鉴网上常见的远程更新QSPI FLASH的相关示例,对表贴式SD卡的应用程序进行了在线更新的操作适配

在本文中,我们将实现其余未实现的层:全连接层、池化层和激活函数 ReLU。

在之前的学习当中,我们已经学习了Vivado的基本操作,接下来我们将继续学习软件的下板验证过程

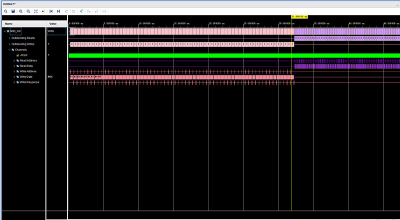

接slave接口篇,本文继续打包一个AXI4-Full-Master接口的IP,学习下源码,再仿真看看波形