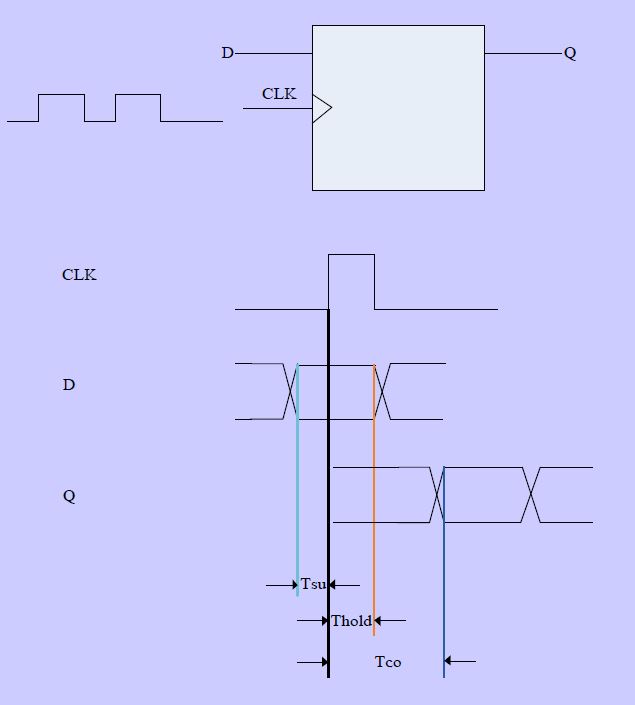

综合时序图:

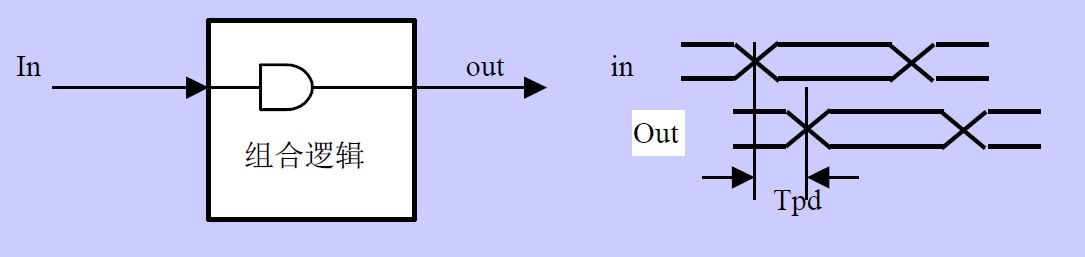

Tpd : propagation delay . I/O pin input to non-registered output delay. The time required for a signal on any I/O pin input to propagate through the combinatorial logic in a macrocell and appear at an external device output pin.

传播延时,即I/O管脚输入到非寄存器输出延时。信号从任何一个I/O脚输入,通过一个宏单元内的组合逻辑后,从另一个管脚输出,所需要的时间。范围:5~12ns。

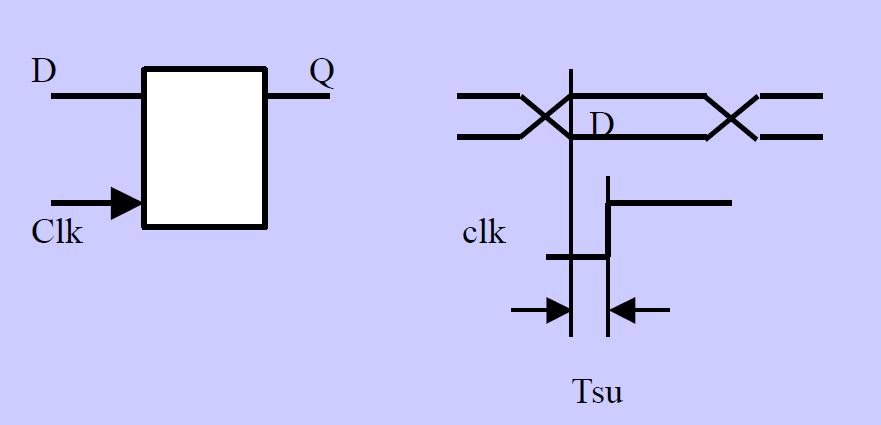

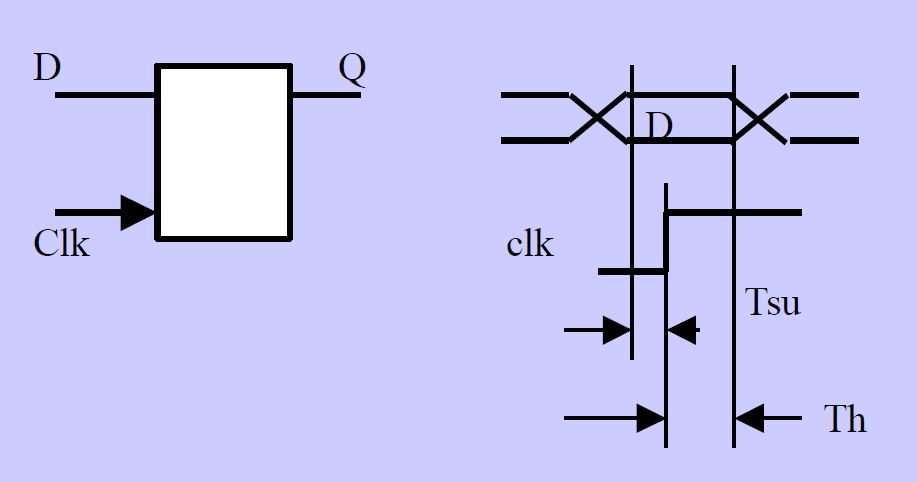

Tsu : Global clock setup time.The time that data must be present at the input pin before the global (synchronous) clock signal is asserted at the clock pin.

全局时钟的建立时间。输入脚的数据必须在全局(同步)时钟有效之前,提前有效的时间。Tsu的范围:2.9~7ns。

Thold:在时钟上跳沿后,Data必须保持的最小时间。

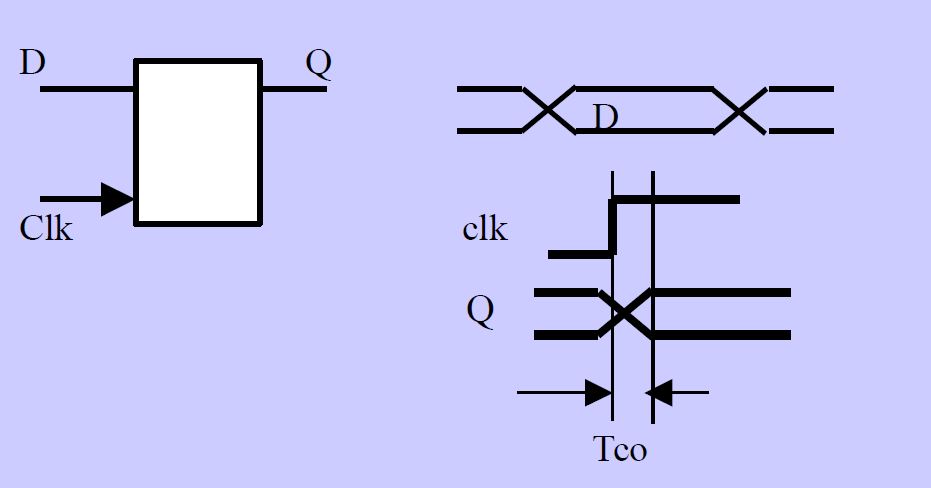

Tco:Global clock to output delay . The time required to obtain a valid output after the global clock is asserted at the clock pin.

时钟上升沿与输出端(Q端)数据稳定输出的时间差。

版权声明:本文为CSDN博主「JohnHe1994」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/johnhe1994/article/details/79641280