为什么要进行管脚约束。

刚做项目的时候,往往会忽略IO口的约束。每次稍微改动一些东西,就会发现 编译的结果不是自己想要的。 这样的现象一般来说,就是时序有问题。 一般 逻辑代码的约束还好做, IO口的约束有些麻烦。

解释一个名词。

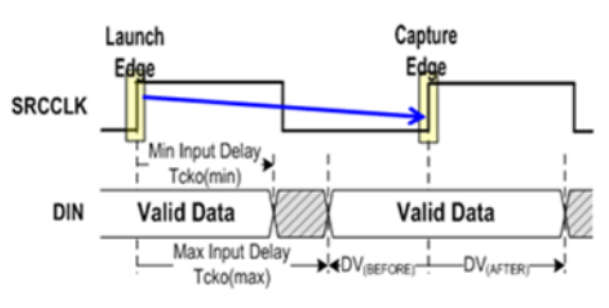

为了改进系统同步接口中时钟频率受限的弊端,一种针对高速I/O的同步时序接口应运而生,在发送端将数据和时钟同步传输,在接收端用时钟沿脉冲来对数据进行锁存,重新使数据与时钟同步,这种电路就是源同步接口电路(Source Synchronous Interface)。 在我们这边的设计中, 在IO设计中,经常要用到 源同步时钟。

input_delay.

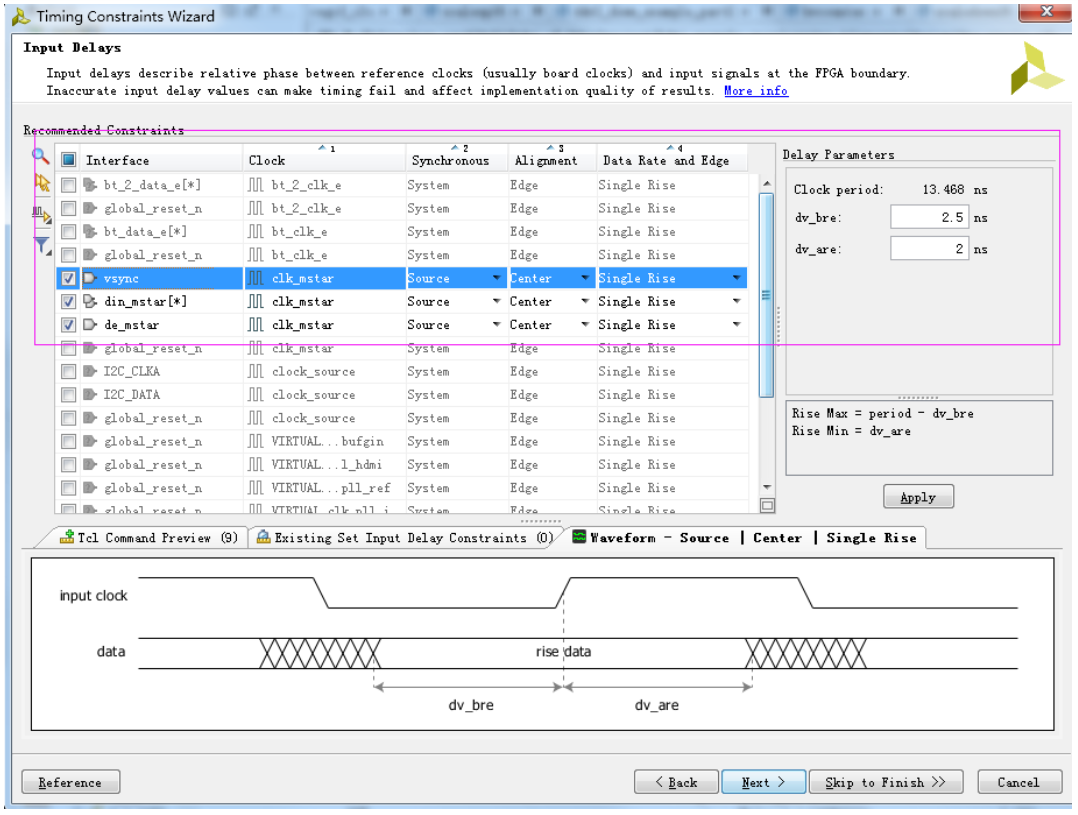

在我们的设计中 setup 为2.5ns. hold on为 2.0ns,时钟周期是 13.468ns. 在不考虑 时钟 有jitter跟skew的存在,那么 在 vivado 里面应该这么设置。

那么 在xdc 文件中会出现 这样的Input delay 约束。

set_input_delay -clock [get_clocks clk_mstar] -min -add_delay 2.000 [get_ports {din_mstar[*]}]

set_input_delay -clock [get_clocks clk_mstar] -max -add_delay 10.968 [get_ports {din_mstar[*]}]

set_input_delay -clock [get_clocks clk_mstar] -min -add_delay 2.000 [get_ports de_mstar]

set_input_delay -clock [get_clocks clk_mstar] -max -add_delay 10.968 [get_ports de_mstar]

set_input_delay -clock [get_clocks clk_mstar] -min -add_delay 2.000 [get_ports vsync]

set_input_delay -clock [get_clocks clk_mstar] -max -add_delay 10.968 [get_ports vsync]

关于 Output delays 设置。

在 vivado 中, 关于 时钟的输出,一定要用 ODDR 。这样才会出现 Forwarded Clocks.

ODDR #(

.DDR_CLK_EDGE("SAME_EDGE"),

.INIT(1'b0),

.SRTYPE("SYNC") )

ODDR_inst_a (

.Q(IDCK_OUTA),

.C(clk_out_a),

.CE(1'b1),

.D2(1'b1),

.D1(1'b0),

.R(1'b0),

.S(1'b0));

时钟周期 是 6.734ns. 下游芯片的 setup 是 1.5ns , hold on 是 1ns. 假如 数据 和 时钟的 pcb 布线是 严格等长的。

这时候 xdc文件中会出现这样的约束。

set_output_delay -clock [get_clocks IDCK_2_OUTA] -min -add_delay -1.000 [get_ports {D_OUTE[*]}]

set_output_delay -clock [get_clocks IDCK_2_OUTA] -max -add_delay 1.500 [get_ports {D_OUTE[*]}]

这样 input 和 output 的时序约束,基本上就做好了!!!!

版权声明:本文为CSDN博主「angelbosj」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/angelbosj/article/details/52921563