本文转载自: 傅里叶的猫微信公众号

本文整理自Xilinx公开课:Vivado时序收敛技术。

有些知识在公开课中讲的并不是很细,因此我又对齐进行了整理,分为了几篇文章。

有很多内容也在我的时序约束课程中讲到过,都是免费课程,大家可以在公众号上找到。

如果出现了时序违例,我们会关注两点:

1. 为什么会出现时序违例?

2. 如何解决?

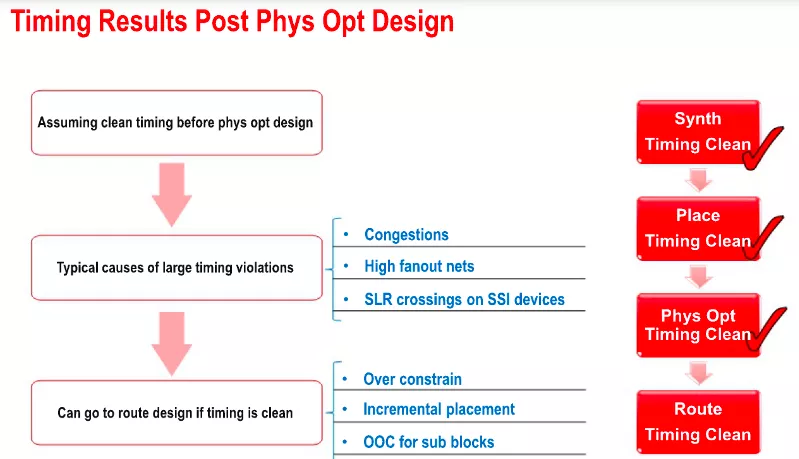

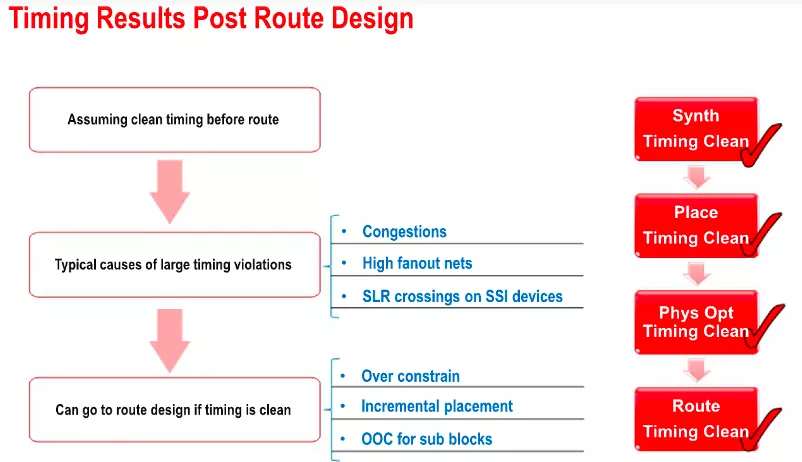

首先我们要搞清楚时序是在哪个阶段违例:

在综合阶段或者post opt阶段出现了时序违例,那么很有可能的原因如下:

前三个的解决方案都类似,就是进行正确的时序约束和正确的综合选项设置;如果是电路设计延时太高,电路中级联的级数太多,那么就要修改设计了。这里有一个经验值,就是LUT+NET的延时是0.5ns,如果时钟周期为5ns,那电路中最大的级联数为5ns/0.5ns=10级。

在Place阶段出现了时序违例,那么很有可能是:

在Place Opt阶段出现了时序违例,很有可能是:

此时我们可以采取的措施包括: