本文转载自: FPGA打工人微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

之前通过发布的文章是真实的(文章是描述的)命令命令在上面的实际情况下使用的。在实现的每个子结束后打印至指定日志文件。

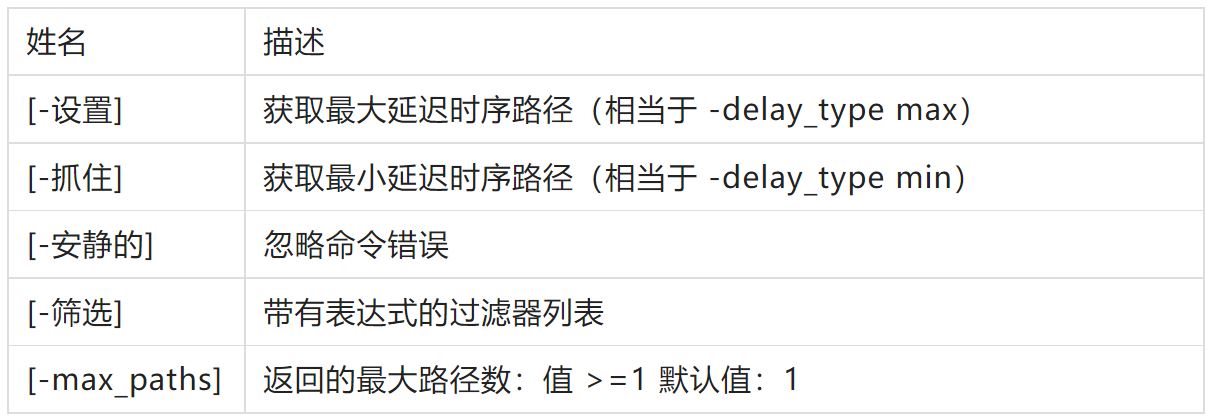

可能会get_timing_paths命令

get_timing_paths [‑from

[‑to

[‑rise_through

[‑setup] [‑hold] [‑max_paths

[‑slack_lesser_than

[‑no_report_unconstrained] [‑user_ignored] [‑routable_nets]

[‑sort_by

[‑quiet] [‑verbose]

该命令的参数是真实的多,只用了几个

在使用过程中,将其封装成一个子函数使用

proc write_status {text statusfile} {

set fid [open ${statusfile} a+]

set wns [get_property SLACK [get_timing_paths -setup -quiet]]

set whs [get_property SLACK [get_timing_paths -hold -quiet]]

set tns 0

set ths 0

foreach tp [get_timing_paths -setup -quiet -max_paths 100000 -filter {SLACK < 0}] {

set tns [expr ${tns} + [get_property SLACK ${tp}]]

}

foreach tp [get_timing_paths -hold -quiet -max_paths 100000 -filter {SLACK < 0}] {

set ths [expr ${ths} + [get_property SLACK ${tp}]]

}

set setup "WNS=[format {%2.3f} ${wns}] / TNS=[format {%2.3f} ${tns}]"

set hold "WHS=[format {%2.3f} ${whs}] / THS=[format {%2.3f} ${ths}]"

puts ${fid} "VIVADO timing ${test}: ${setup} - ${hold}"

close ${fid}

}

tcl的常用语法可以参考我前面关于tcl的几篇文章,从代码中可以输入参数,主要有两个参数,一个是us文件,另一个是stat文件。 ,statusfile 是打印在哪个日志文件,具体的使用如下:

opt_design -directive ExploreWithRemap

write_status "opt_design ExploreWithRemap" ./work/vivado_timing.log

它的功能/选择_设计后的定时打印置。中,方便使用/查看。