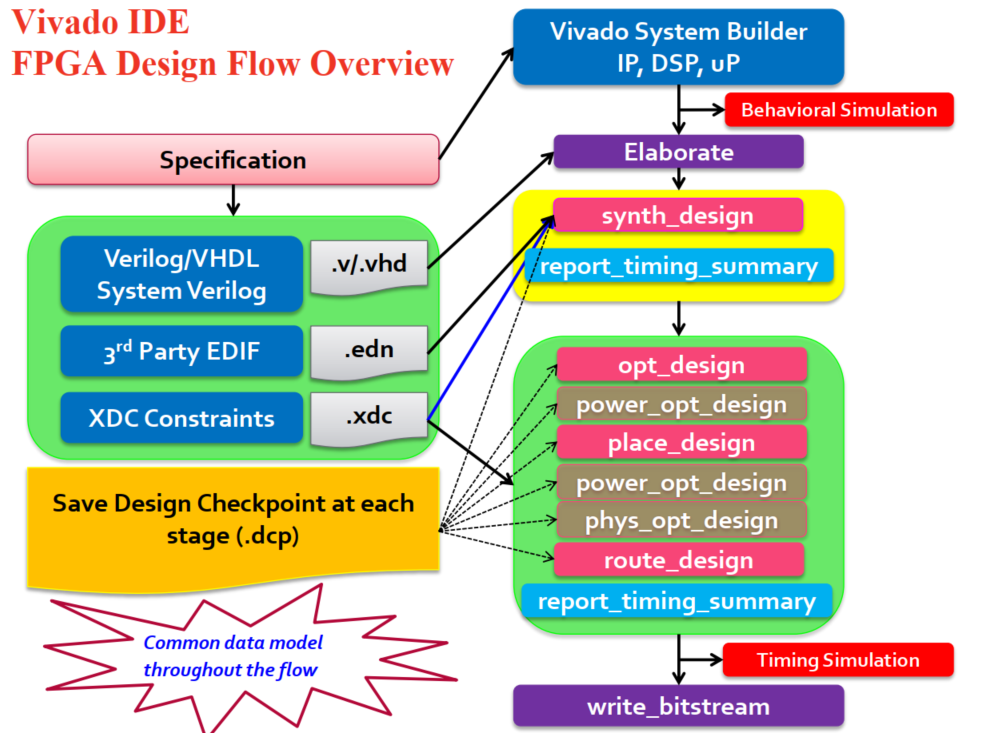

Vivado设计流程

使用Vivado进行设计开发的步骤如下:

1. 功能设计:使用HDL语言设计、自带或者第三方的IP、嵌入式处理器等。

2. 综合:在综合时可以加入第三方的网表文件和约束文件。

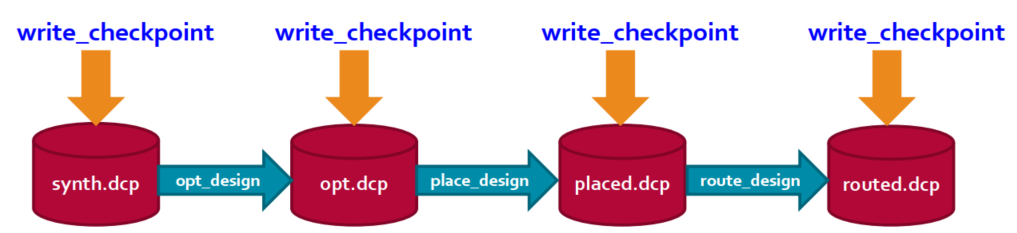

3. 实现:在Vivado实现的步骤中,必须要执行的有三个opt_design、place_design、route_design。

在设计过程中,各个阶段的生成的文件都是.dcp,Vivado使用的是通用的模型贯穿在设计。

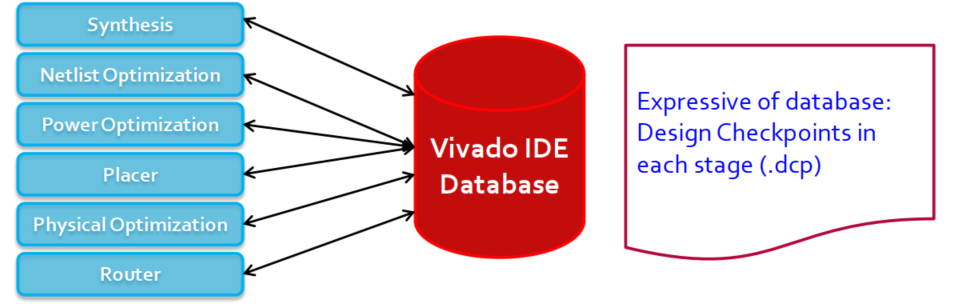

Checkpoint文件

Checkpoint文件是Vivado运行工程设计后存储的信息及设计相关文件的文件格式,同时也是Vivado中使用的通用数据库,在Checkpoint中包含:

网表:Logical Netlist (EDIF)

约束:Constraints (XDC)

物理数据:Physical Data (XDEF)

不同情况下,不同dcp用到的网表文件可能不同。

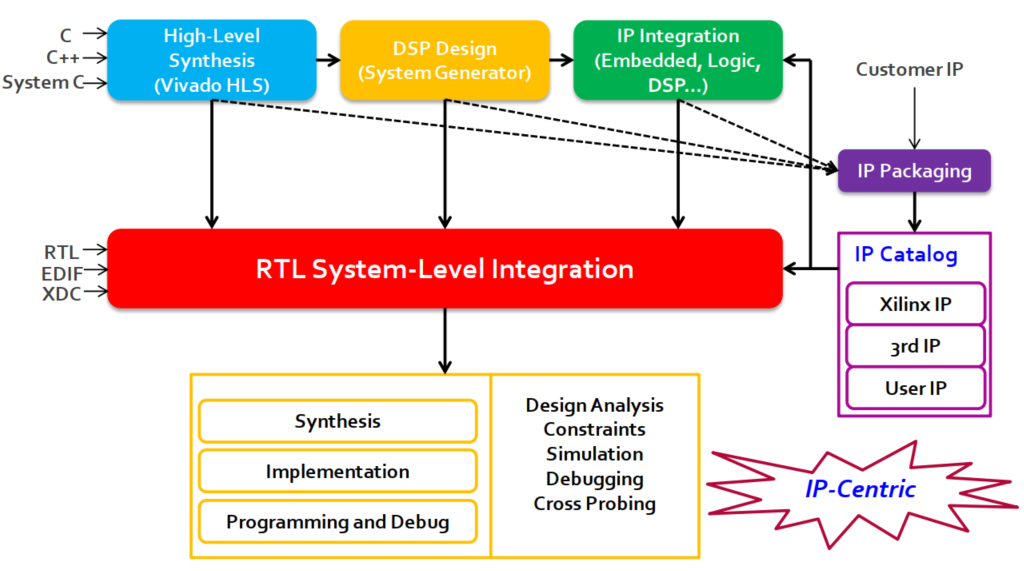

Vivado设计理念是以IP为核心,使用过Vivado的人都知道在vivado中有block design这个类似画布的东西,在这个界面里可以把IP进行嵌入,通过鼠标进行连接链路,搭建属于自己的数字积木。

综合

综合是FPGA设计中不可缺少的环节,综合就是把HDL语言/设计转换为综合网表的过程。综合网表会包含已经转化后的逻辑设计所对应的资源模块,包括组合逻辑器件、寄存器,FPGA特有的各种原语(Primitive),内部的硬核模块等,同时会描述这些模块的属性和约束信息。

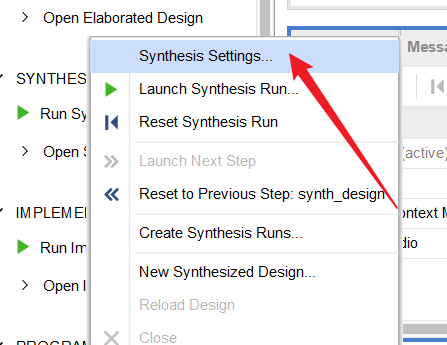

打开vivado后,右键综合选项,可以配置该工程的综合设计。

在综合设置中,可以根据实际需求进行设定综合的约束文件,综合策略,以及制定综合过程的相关优化策略。

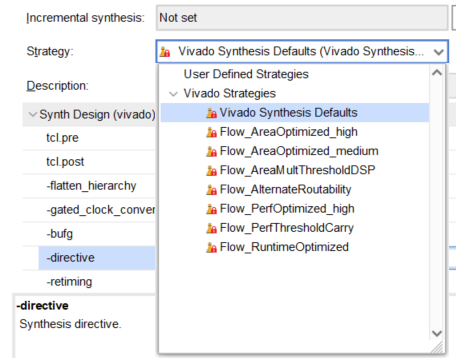

综合选项使用分析(vivado 2020.2)

可以对综合进行不同优化策略设计,使得设计满足相应的需求。

下面对上述综合设计中的选项进行分析说明:

tcl.pre:可以进行指定综合前所运行的tcl脚本。

tcl.post:可以进行指定综合后所运行的tcl脚本。

none

该选项指示综合工具永远不会使层次结构改变,一些边界优化将无法进行。

综合的输出将具有与原始RTL完全相同的层次结构。

full

该选项指示工具将层次结构完全打平,只留下顶层,综合后的网表文件只有一个顶层。

Rebuilt

这是默认的flat _hierarchy选项。

Rebuilt选项允许工具扁平化层次结构,执行综合,然后重建基于原始RTL的层次结构。

Rebuilt选项允许跨边界优化,且最终的层次结构是与RTL相似,以方便分析。

-gate_clock_conversion

用于管理门控时钟(Gated Clock),门控时钟是指由门电路而非专用时钟模块例如MMCM或PLL生成的时钟。门控时钟会给设计带来一些负面影响,可通过-gated_clock_conversion移除,当时钟负载少且时钟频率低时比如小于5MHz,可以适当利用门控时钟(建议手工插入BUFG)。

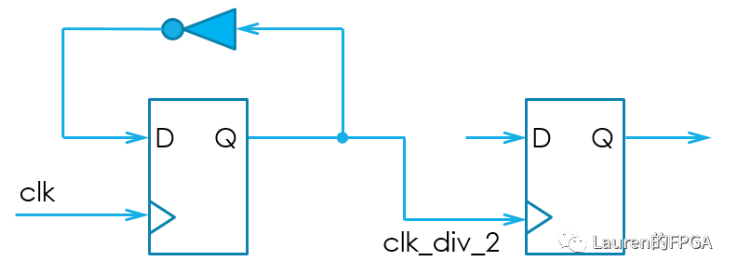

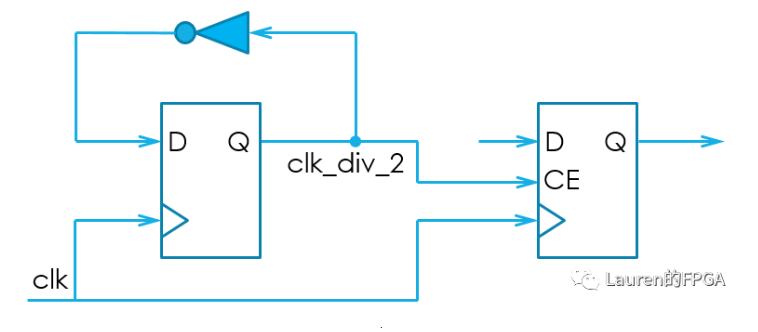

一个典型的门控时钟如下图所示,即触发器和反相器构成的二分频电路。此时,若第一个触发器的Q端对应的信号clk_div_2被其他逻辑用做时钟,那么就构成了门控时钟电路。

门控时钟会对设计带来一些负面影响。典型的危害包括:时钟信号可能会有毛刺;时钟歪斜(Clock Skew)会恶化。同时,一个不可忽略的影响是Vivado并不会对门控时钟主动插入BUFG,这就意味着该时钟会占用传统的布线资源也就是Fabric中的布线资源而不会使用时钟网络资源,从而可能会跟其他关键路径争夺布线资源,影响时序。

-gated_clock_conversion可将门控时钟信号变为使能信号,对于上图所示门控电路,Vivado可将其优化为下图所示电路。此时,clk_div_2被转化为使能信号连接到了下级触发器的使能端口,而下级触发器的时钟端口则与主时钟clk连接,从而移除了门控时钟。

-directive

可以指定综合时的使用相关优化指令,可以针对性的去进行优化设计。

RuntimeOptimized:执行最短时间的优化选项,会忽略一些RTL优化来减少综合运行时间。

AreaOptimized_high/medium:执行一些通用的面积优化。

AlternateRoutability:使用算法提高布线能力,减少MUXF和CARRY的使用。

AreaMapLargeShiftRegToBRAM:将大型的移位寄存器用块RAM来实现。

AreaMultThresholdDSP:会更多地使用DSP块资源。

FewerCarryChains:位宽较大的操作数使用查找表(LUT)实现,而不用进位链。

-retiming

寻求通过组合门或LUTS自动调整寄存器(寄存器平衡)来改善时钟内顺序路径的电路性能。它维护电路的原始行为和延迟,不需要对RTL源进行更改。

有两种不同的重定时方法,向后重定时和向前重定时。向后重定时从门的输出中删除寄存器,并在同一逻辑门的输入出创建新的寄存器。向前重定时的作用正好相反,它从逻辑门的输入中删除寄存器,并在输出中创建新的寄存器。

在Vivado 综合操作中有两种方法实现自动重定时:全局重定时和局部重定时。

全局重定时是对整个设计而言的,基于设计时的时序要求优化大型组合逻辑结构中的寄存器设计。

这种方式需要分析设计中的所有逻辑,优化最坏路径情况下的寄存器从而使整体设计反应速度更快。为了实现这一点设计时必须在.xdc文件中规定准确的时间限制。在synth_design或Vivado GUI综合设置下通过-retiming命令启用全局重定时,此外该特性还可以与合成中的BLOCK_SYNTH特性一起用于设计中的特定模块。

局部重定时是指用户明确告诉工具使用retiming_forward、retiming_bbackward RTL属性时需要执行的重定时逻辑。

指定使用最大个数

该部分都是指定相关资源使用的最大个数的设置选项

-bufg:指定全局时钟的buffers最大使用个数。

-max_bram:指定bram最大使用个数。

-max_uram:指定ultra ram最大使用个数。

-max_dsp:指定dsp最大使用个数。

-max_bram_cascade_height:指定bram最大级联使用个数。

-max_uram_cascade_height:指定uram最大级联使用个数。

-no_lc

lc(LUT combining):查找表组合。

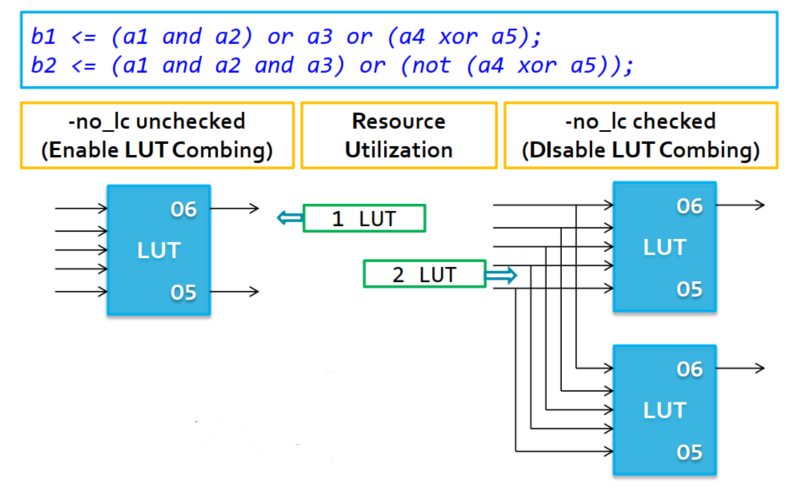

当两个输出都具有同样输入时,若不使能no_lc,则只会消耗一份LUT资源,如果使能no_lc,则会消耗两份LUT资源。

例如下图:

乍一看,如果不使能no_lc的check,这样不是更节省资源吗?

不进行no_lc的check,LUT组合利用双输出LUT(O5、O6)进行设计逻辑,确实可以节省资源,减小面积,但是带来的代价是可能造成布线的堵塞,而使用no_lc的check,将两个输出综合成两个LUT,位置比较灵活,这样可以方便工具进行优化布线。

对于Vivado来说,默认是禁用 LUT combine,XST/Synplify 工具默认是使能 LUT combine 。

赛灵思指导建议

如果O5、O6同时使用的LUT占比大于了15%, 建议在关闭LUT combining。

-fsm_extraction

用于设定状态机的编码方式,其可选值为one_hot, sequential, johnson, gray, auto和off。默认值为auto,此时Vivado会自行决定最佳的编码方式。

-keep_equivalent_registers

等效寄存器,即共享输入数据的寄存器。勾选时,等效寄存器不合并;不勾选时,等效寄存器合并。等效寄存器可以有效的降低扇出,可以通过综合属性keep避免其被合并。

-resource_sharing

设置不同信号间共享算数操作符,选择为auto时设计会根据设计时序判断是否进行资源共享。

-control_set_opt_threshold

为控制信号(不包括时钟)的扇出个数,表明对小于此值的同步信号进行优化,显然此值越大,被优化的触发器越多,但占用的查找表也越多。若此值为0,则不进行优化。通常情况下,按默认值auto运行即可。

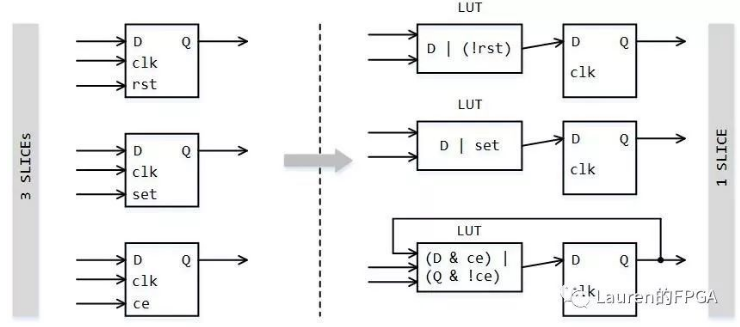

触发器的控制集由时钟信号、复位/置位信号和使能信号构成,通常只有{clk,rst/set,ce}均相同的触发器才可以被放置在一个SLICE中。但是,对于同步置位、同步复位和同步使能信号,Vivado会根据-control_set_opt_threshold的设置进行优化,其目的是减少控制集的个数。优化的方法如下图所示。在优化之前,3个触发器被分别放置在3个SLICE中,而优化后,被放置在1个SLICE中,但此时需占用查找表资源。

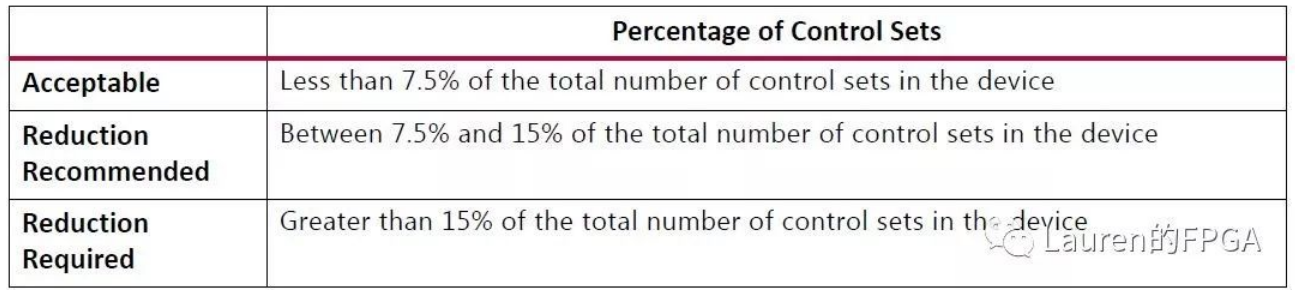

UG949(V2017.4版本)Table 5-9 给出了控制集的百分比(适用于7系列FPGA和UltraScale FPGA),如下图所示。可以看到当这个百分比超过15%时,表明需要降低控制集。

-shreg_min_size

-shreg_min_size

当移位寄存器深度小于等于-shreg_min_size时,最终实现方式为触发器级联的形式;而当其深度大于-shreg_min_size时,实现方式则为FF + LUT + FF的形式。

-no_srlextract

选中该选项时,移位寄存器会用普通的寄存器实现,而不用FPGA内部专用的SRL资源。-no_srlextract则是阻止工具将移位寄存器映射为LUT,其优先级高于-shreg_min_size。例如,当移位寄存器深度为4,-shreg_min_size为3,-no_srlextract被勾选,那么最终实现形式是4个触发器级联的形式,而非FF + LUT + FF的形式。

-cascade_dsp

设置在求DSP块输出总数时使用多少个加法器,默认计算时会使用块内部的加法器链。设置为tree会强制将该计算在fabric结构中实现。

-assert

将VHDL中的assert状态纳入评估。失败或错误级别会停止综合进程并产生一个错误信息;警报级别会产生一个警告信息。

设计中常用的一些综合属性

移位寄存器

Xilinx 7系列的FPGA在实现移位寄存器,使用单个查找表(LUT)中实现的1到32个时钟周期移位寄存器。使用srl_style可对移位寄存器生成的结构进行不同类型的描述。

使用srl_style只需在设计的V文件中的目标寄存器前加上如下代码即可:

(* srl_style = "XXX" *) reg [WIDTH-1:0]shift_reg;

srl_style中可填入5种不同的值,填入不同值后,会生成不同的结构。

(* srl_style = “srl_reg” *),将会描述移位寄存器为SRL + FF结构。

(* srl_style = “reg_srl” *),将会描述移位寄存器为FF + SRL结构。

(* srl_style = “reg_srl_reg” *),将会描述移位寄存器为FF + SRL + FF 结构。

(* srl_style = “register” *),将会描述移位寄存器为纯FF结构。

(* srl_style = “srl” *),将会描述移位寄存器为纯SRL结构。

使用SRL好处

使用SRL可以有效减小面积,因为使用单个查找表(LUT)中实现的1到32个时钟周期移位寄存器。并且使用SRL相比级联寄存器的结构性能要更好(支持的最高频率更高)。

SRL+ FF结构的好处

触发器的时钟到输出时间远低于SRL的时钟到输出时间,这就是为什么在SRL的输出中添加触发器的原因。

RAM和ROM

使用(* ram_style = "distributed or block" *) ,可以

指导Vivado综合工具如何推断存储器资源的类型。

可使用distributed or block,描述存储器资源

distributed :指示工具推断LUT ram,将此属性放在为RAM声明的数组上。

block:指示工具推断RAMB类型组件。

DSP48

在模块或者寄存器中指定使用如,(*use_dsp48=“yes”*),可使得该部分的算术运算使用dsp资源进行实现。

在默认的情况下,如下的算术类型结构会综合成DSP48E资源:

1. 乘法

2. 乘加操作

3. 乘减操作

4. 乘累加操作

其余的加法,减法,累加则会默认使用逻辑资源去实现。该属性会覆盖默认行为并强制将这些结构强制转换为DSP48块,并将其置于RTL中signals,architectures和components,entities和module上,具有以下优先级:

Signals > Architectures and components > Modules and entities

dont_touch

使用dont_touch可以防止相关内容被逻辑优化,此属性可以放置在任何信号、模块、实体或组件上。例如:

(* dont_touch = "true" *) wire sig1;

reference