本文转载自:FPGA技术实战的CSDN博客

引言:传输介质的选择,无论是PCB材料还是电缆类型,都会对系统性能产生很大的影响。尽管任何传输介质在GHz频率都是有损的,但本章提供了一些管理信号衰减的指南,以便为给定的应用获得最佳性能。

1.信号实际频率

信号边缘包含称为谐波的频率分量。每个谐波都是信号频率的倍数,其有效最高频率可以由式1表示:

由于PCB中的介电损耗与频率有关,因此必须确定所关注的带宽以找到PCB的总损耗。频率必须从工作频率开始,并延伸至等式1中的频率。例如,具有10ps上升时间的10Gb/s信号具有10Ghz到35Ghz的带宽。

2.介质损耗

电介质中损耗的信号能量是材料特性的函数。用来描述材料的一些参数包括相对介电常数(也称为介电常数)和损耗角正切。集肤效应也是在GHz范围内能量损失的一个因素。

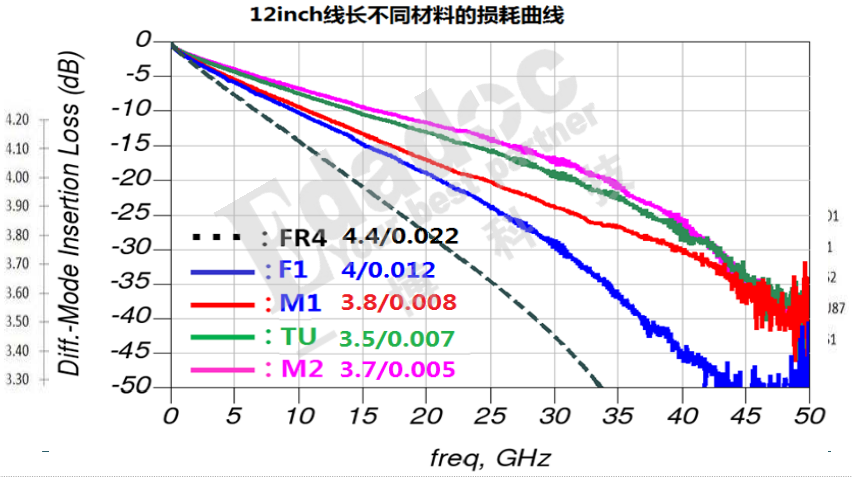

图1、不同材料的损耗曲线

2.1 相对介电常数

相对介电常数是测量介质对导体电容的影响。相对介电常数越高,信号在PCB走线传播的速度越慢,给定走线几何结构的阻抗越低。低常数εr几乎总是首选。

相对介电常数

尽管在所有材料中,相对介电常数随频率变化,但FR4的εr随频率变化很大。由于εr直接影响阻抗,FR4走线阻抗值随频率的增加而扩展。虽然在1.125 Gb/s的速度下,这个扩展可能不重要,但在10Gb/s的速度下,它可能是一个问题。

损耗角正切

损耗角正切是一种测量电介质沿传输线传播时,有多少电磁能量损失到电介质上的方法。较低的损耗角正切允许更多的能量以较少的信号衰减到达目的地。

随着频率的增加,能量损失的幅度也随之增加,导致信号边缘的最高频率谐波受到最大的衰减。这表现为上升和下降时间的下降。

集肤效应和电阻损耗

集肤效应是电流优先在导体外表面附近流动的趋势。这主要是由于高频信号中的磁场推动电流沿垂直方向流向导体的周长。

随着表面附近电流密度的增加,电流流过的有效横截面积减小。由于导体的有效横截面积现在变小,所以电阻增大。因为这种趋肤效应随着频率的增加而更加明显,电阻损耗随着信号速率的增加而增加。

电阻损耗对信号的影响与损耗角正切相似。由于高次谐波的振幅减小,上升和下降时间增加,最高频率的谐波受到的影响最大。在10Gb/s信号的情况下,使用FR4时,即使基频也会有一定程度的衰减。

例如,在1 MHz下8 mil宽的走线的电阻约为0.06Ω/英寸,而在10Gb/s下相同的走线的电阻略高于1Ω/英寸。给定一个10英寸的走线和1.6V的电压摆幅,160mV的电压降是由基频的电阻损耗引起的,不包括谐波和介电损耗中的损耗。

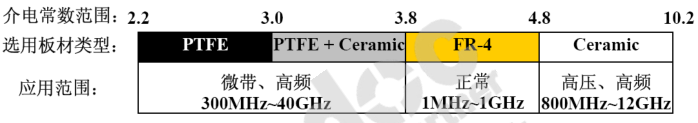

图2、介电常数、板材及应用频率范围

选择基底材料

材料选择的目标是优化特定应用的性能和成本。

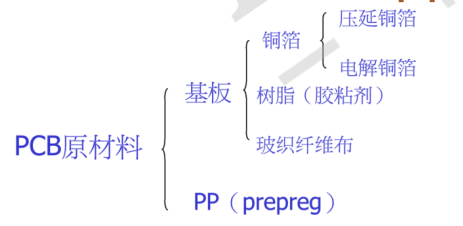

图3、PCB原材料

FR4是最常见的PCB基板材料,通过仔细的系统设计提供了良好的性能。对于较长的走线长度或高信号速率,必须使用具有较低介电损耗的更昂贵的衬底材料。

基板,例如,Nelco,具有较低的介电损耗,并且在GHz范围内表现出显著较少的衰减,因此增加了PCB的最大带宽。在3.125Gb/s时,与FR4相比,Nelco的优点是增加了电压摆幅裕度和更长的Z走线长度。在10Gb/s的速度下,除非高速走线保持很短,否则像Nelco这样的低损耗电介质是必要的。

基板材料的选择取决于高速走线的总长度和信号速率。

假设分析可以在HSPICE模拟中进行,以评估各种基底材料。通过改变PCB基板材料的介电常数、损耗角正切等参数。对眼图质量的影响可以仿真,以证明使用更高成本的材料是合理的。还可以探讨铜板厚度等其他参数的影响。

3.走线

3.1 走线几何

对于任何走线,其特性阻抗取决于其层叠几何结构以及走线几何结构。在差分走线的情况下,紧耦合对之间的电感和电容耦合也决定了走线的特性阻抗。

走线的阻抗由其与附近导体的电感和电容耦合决定。例如,这些导体可以是平面、过孔、焊盘、连接器和其他走线,包括差分对中的其他紧密耦合走线。基板特性、导体特性、磁链面积和到附近导体的距离决定了耦合量,从而决定了对最终阻抗的贡献。

二维场解算器是解决这些复杂相互作用的必要工具,有助于计算走线的最终阻抗。它们也是验证现有走线几何图形的有用工具。

更宽的走线为电流流动创造了更大的横截面积,并减少了高速接口中的电阻损耗。使用空间限制允许的最宽走线。因为走线宽度公差是用绝对值表示的,所以较宽的走线也会使制造走线的百分比变化最小化,从而使沿传输线长度的阻抗控制更加严格。

有时,带状线优于微带线,因为走线两侧的基准面提供辐射屏蔽。微带线只在一侧(通过基准面)被屏蔽,因为它们运行在最顶层或最底层,而另一侧暴露在环境中。

为获得最佳结果,建议使用2D或3D场解算器进行验证。

3.2 高速收发器的走线特性阻抗设计

因为收发器使用差分信号,所以最有用的走线配置是差分边缘耦合带状线和差分微带。虽然有些背板使用差分宽带耦合带线配置,但不建议将其用于10Gb/s操作,因为P和N过孔是不对称的,并引入共模非理想性。

除少数例外,50Ω特性阻抗(Z0)用于通道中的传输线。通常,当宽度/间距(W/S)比大于0.4(8 mil宽的记录道,间隔20 mil)时,P和N信号之间的耦合会影响走线阻抗。在这种情况下,差分走线必须设计为奇数模阻抗(Z0O)为50Ω,导致差分阻抗(ZDIFF)为100Ω,因为ZDIFF=2 x Z0O。

同样的W/S比也必须小于0.8,否则,对于50Ω的Z0O,走线之间的强耦合需要更窄、更损耗的走线。为了澄清,当Z0O为50Ω时,需要60Ω或以下的偶数模阻抗(Z0E)。

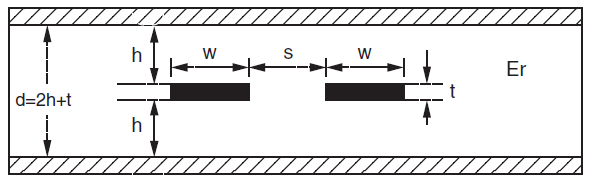

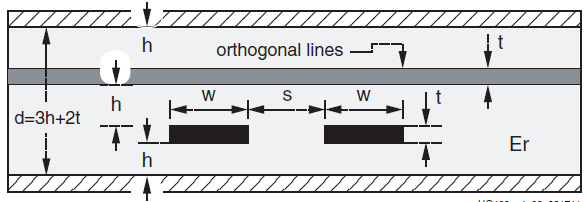

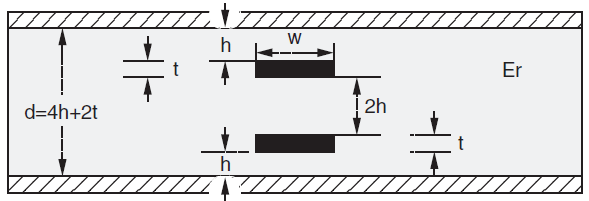

图4至图7显示了差分结构的横截面示例。

图4、差分边缘耦合中心带状线

图5、差分边耦合偏移带状线

图6、中心宽边耦合带状线

图7、差分微带

一个好的印刷电路板制造商了解控制阻抗,并允许对线宽进行微调,以产生50Ω的Z0O。PCB制造商还提供特定PCB布局所需的参数。一些参数可以根据示例中概述的准则进行计算或仿真。尽管Z0O上±10%的公差是典型的,并且可以提供足够的性能,但是更紧公差的额外成本会导致更好的信道性能。

3.3走线布线

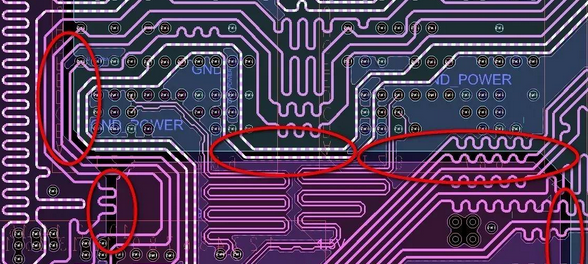

高速串行差分走线应以最高优先级布线,以确保对这些关键走线提供最佳路径。这减少了对弯曲和通孔的需要,并将阻抗转换的可能性降至最低。走线必须保持笔直、简短,并尽可能减少层叠变化。过孔的影响在后续的微分过孔中讨论。

高速走线的布线必须避免靠近其他走线或其他潜在噪声源。相邻信号平面上的走线应垂直运行,以尽量减少串扰。

尽可能使用带状线,以及最上面和最下面的带状线层,以尽量减少通孔短线。规划层叠时,这些层必须尽可能靠近顶层和底层可能。设计限制可能需要用于BGA出口路径或从通孔到连接器传输或SMT焊盘的微带线。在这种情况下,微带线必须尽可能短。

建议使用斜接45度弯头(与90度弯头相反)。在90度弯曲处,走线的有效宽度发生变化,由于附加导体区域与基准面的电容耦合,导致阻抗不连续。差分对的两条走线必须长度匹配以消除偏差。歪斜在共模中产生不匹配,并因此降低差分电压摆幅。

3.4 平面分割

地平面应作为信号的参考平面,而不是噪声较大的电源平面。每个参考平面在走线长度上应该是连续的,因为在平面分割上布线会产生阻抗不连续性。在这种情况下,走线的阻抗会发生变化,因为其与基准面的耦合在平面分割处发生突变。

图8、PCB走线跨分割平面

3.5 回流

在平面分割上布线也会产生回流问题。由于介电损耗中提到的集肤效应,高速信号在走线表面附近传输。同时,回流也在紧耦合参考面的表面附近流动。

由于紧密耦合,回流有向原始信号传输走线靠近的趋势。在平面分割时,回流不能再沿着与走线平行的同一路径,而是必须找到另一条路径。

平面分割会导致次优的电流返回路径,并增加电流回路面积,从而增加平面分割出走线的电感,从而改变走线的阻抗。

3.6 有损传输线

由于各种电路仿真器使用不同的建模实现(频域和时域技术),因此检查模型是否准确反映实际损耗非常重要。一种方法是将模型与已知的已发布配置进行比较。

4.电缆

图9、常见高速连接器

由于沿电缆长度方向导体和电介质的物理尺寸恒定,电缆是受控阻抗传输线。最高质量的电缆在这些尺寸上几乎没有变化,并且在高频下具有低损耗的宽带宽。

4.1 连接器

连接到电缆的连接器应具有低寄生电感、低寄生电容和低串扰,以实现高带宽操作。

4.2 导线间偏移

选择电缆时,请查看电缆中导线之间的倾斜规格。如果导线长度不匹配,则共模中会出现偏移,并直接降低眼图高度。