作者:FPGA入门到精通

AXI4协议广泛应用于FPGA和ASIC设计中,特别是在需要高速数据传输和复杂系统架构的场合,比如DDR、PCIE、音视频处理IP等等,对于FPGA开发者需要熟练掌握这套协议。

一、AXI4的特点

1、独立的读写通道

AXI4协议包含五个独立的通道:读地址通道、写地址通道、读数据通道、写数据通道和写响应通道。

这种通道分离特性使得控制、地址信息和数据信息无固定的相位关系,有利于流水线操作和提升传输效率。

2、支持突发传输

AXI4支持突发式传输,这意味着可以一次性传输多个数据,而不需要为每个数据传输单独指定地址。

这种特性特别适用于需要高速数据传输的场景,如处理器访问存储器。

3、乱序数据包收发

AXI4允许在未收到回应时发送多个待执行操作的地址信息,当多个slave操作完成时间不一致时,完成顺序与Master的控制顺序可以不同,从而提高了系统的性能。

4、支持非对齐数据传输

AXI4支持非对齐数据传输,即数据可以在任意地址开始传输,这对于处理不规则数据分布的场景非常有用。

5、地址/控制信号与数据分离

AXI4的地址/控制信号与数据处于不同阶段,这使得可以同时传输地址、控制信息和数据,进一步提高了传输效率。

二、AXI4 接口类型

AXI4协议支持三种类型的接口:

1、AXI4(AXI4-full)

面向高性能地址映射通信的需求,允许最大256轮的数据突发传输。

支持突发传输,主要用于处理器或FPGA访问存储器等高速数据传输场景。

2、AXI4-Lite

轻量级的地址映射单次传输接口,适用于吞吐量较小的通信,不支持突发传输。

主要用于访问一些低速外设中的寄存器。

3、AXI4-Stream

面向高速流数据传输,不需要地址映射,允许无限制的数据突发传输规模。

与FIFO一样,根据握手机制,连续发送数据流,主要用于如视频、PCIe、DMA 接口等需要高速数据流传输的场景。

三、AXI4 握手机制

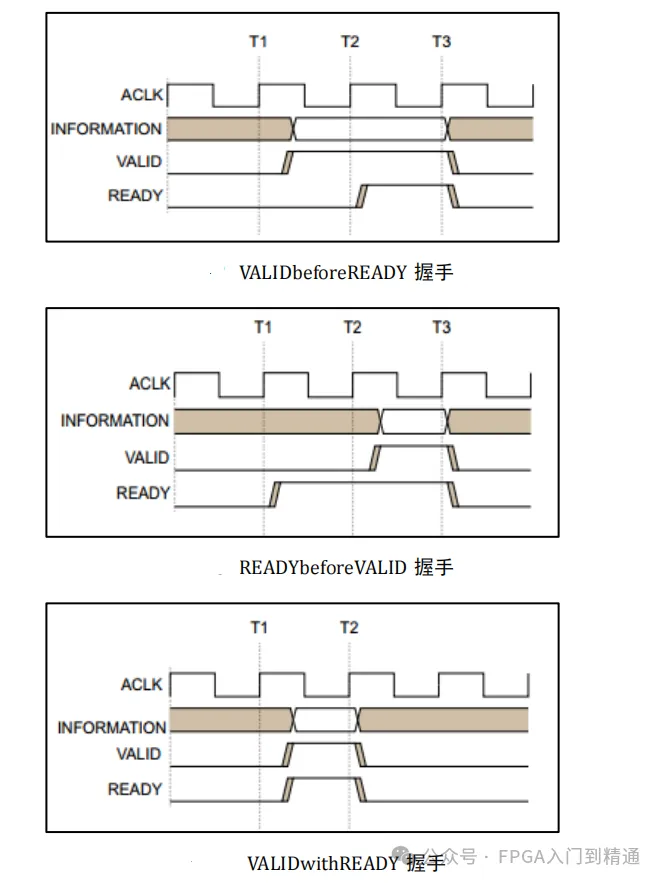

AXI4协议采用READY和VALID握手通信机制,只有READY和VALID都为高时,对应通道的所有信号才有效。

VALID 信号由发送端产生,表示当前地址或者数据是有效的。

READY 信号由接收端产生,则表示当前接收端空闲,已准备好接收信息。

根据VALID和READY的出现时间,可以分为以下3种握手机制:

对于这个握手机制需要注意的理解误区,那就是:

可能出现当前周期下REDAY信号拉高,但下一个周期REDAY信号就拉低了。

发送端在当前周期下READY信号为高时,才能更新下一个数据,且保持VALID信号和DATA信号不变。

四、AXI4 通道

这块了解即可,实际使用时,对于不熟悉的接口再对照手册查看。

AXI4协议包含五个通道,每个通道都有其特定的信号和功能:

1、写地址通道(AW channel)

包含AWVALID, AWADDR, AWREADY信号,用于传输写请求的地址信息。

2、写数据通道(W channel)

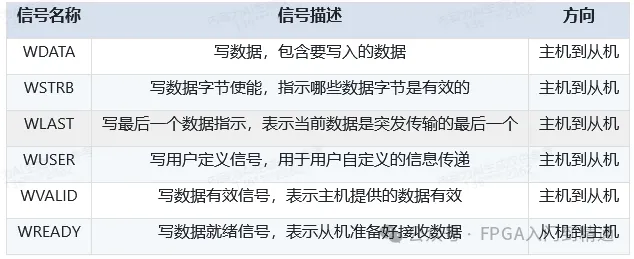

包含WVALID, WDATA, WSTRB, WREADY信号,用于传输写数据及其控制信息。

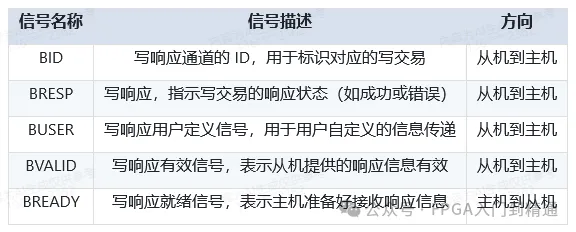

3、写响应通道(B channel)

包含BVALID, BRESP, BREADY信号,用于传输写操作的响应。

4、读地址通道(AR channel)

包含ARVALID, ARADDR, ARREADY号,用于传输读请求的地址信息。

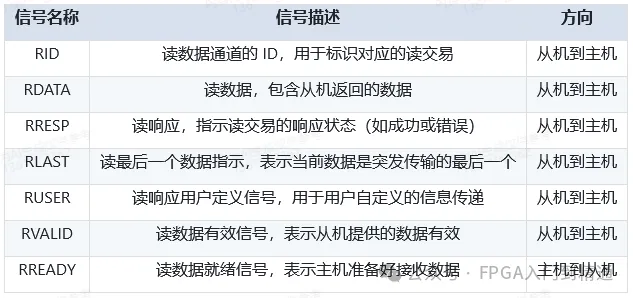

5、读数据通道(R channel)

包含RVALID, RDATA, RREADY, RRESP信号,用于传输读响应的数据和状态。

五、操作时序

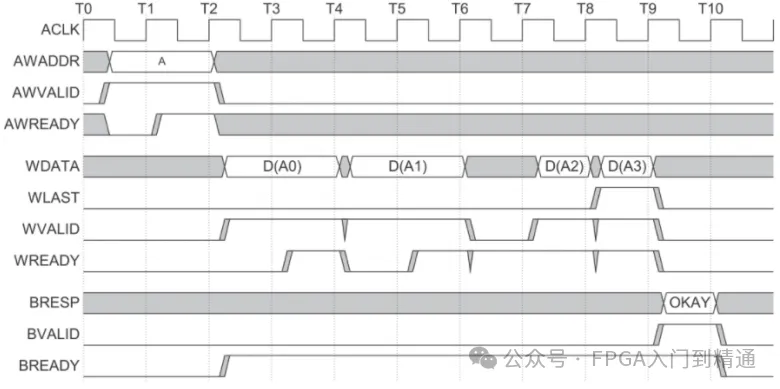

1、突发写时序

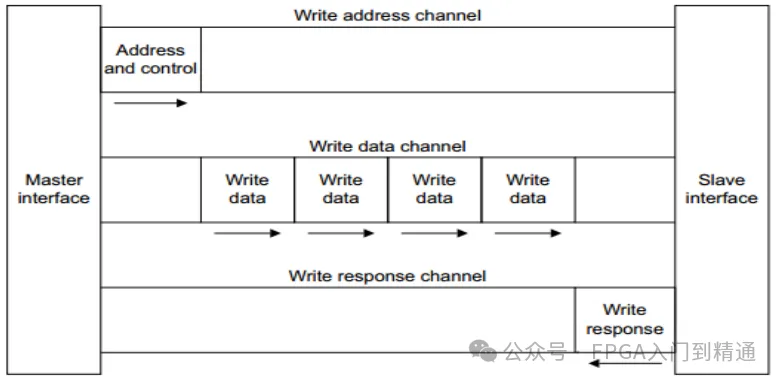

突发写时序需要依次操作“写地址通道”、“写数据通道”、“写响应通道”,传输过程如下图所示:

写数据时序图如下:

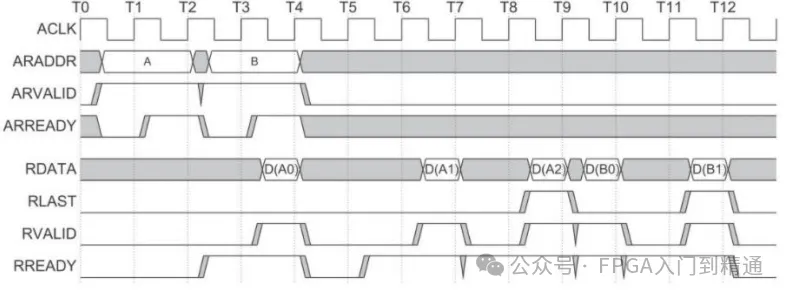

2、突发读时序

突发读时序需要依次操作“读地址通道”、“读数据通道”,传输过程如下图所示:

读数据时序图如下: