作者:张海军 来源:傅里叶的猫

本篇文章参考自Xilinx的白皮书《Xilinx Stacked Silicon Interconnect Technology Delivers Breakthrough FPGA Capacity, Bandwidth, and Power Efficiency》

导言

随着 FPGA 在系统设计中的作用越来越重要,设计也越来越大、越来越复杂,需要更高的逻辑容量和更多的片上资源。迄今为止,FPGA 主要依靠摩尔定律来满足这一需求,每一代新工艺都能提供近两倍的逻辑容量。然而,要满足当今高端市场的需求,摩尔定律的增长所能提供的远远不够。FPGA 开发者都渴望在每一代新 FPGA 中采用容量最大、带宽最高的器件。然而,供应商在产品生命周期的早期制造此类 FPGA 所面临的挑战,可能会限制其向客户提供生产所需的大量器件的能力。这是因为实现可重复编程技术的电路开销会对最大型 FPGA 的可制造性(以及供应)产生负面影响。在新工艺节点的早期阶段,当缺陷密度较高时,随着芯片尺寸的增大,芯片良品率会急剧下降。随着制造工艺的成熟,缺陷密度下降,大型芯片的可制造性显著提高。

因此,虽然最大的 FPGA 在产品推出时供不应求,但随着时间的推移,它们的数量最终会达到支持终端客户批量生产的要求。为了应对可编程需求,一些客户向Xilinx提出挑战,要求Xilinx在产品推出后尽快用最大的 FPGA 来支持他们的批量生产需求。例如,电信市场需要集成数十个Serdes的 FPGA,以提供高信号完整性。设备还需要为数据处理和流量管理提供广泛的互连逻辑和BRAM,同时保持现有的外形尺寸和功耗。为了获得先发优势,设备制造商希望尽快扩大新产品的生产规模。

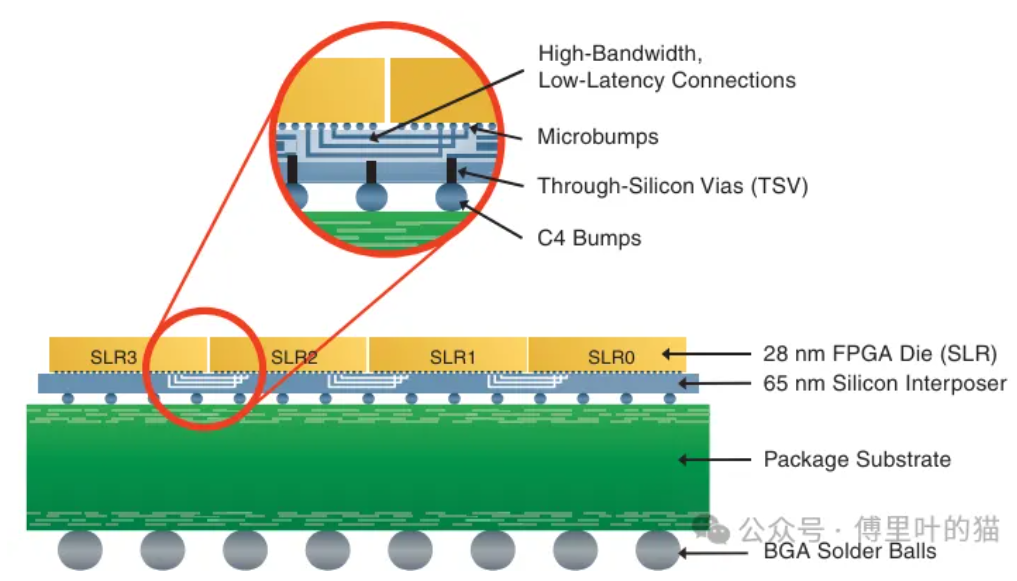

Xilinx针对这些要求,采用创新方法构建 FPGA,其带宽和容量等于或超过最大单片 FPGA 芯片,同时具有较小芯片的制造和上市时间优势,可加快批量生产。这些优势得益于 SSI 技术。通过硅通孔(TSV),可将多个高度可制造的 FPGA 芯片片(称为超级逻辑区域(SLR))组合在单个封装中。该技术还允许不同类型或硅工艺的裸片在插接器上相互连接。这种结构被称为异构 FPGA。

多FPGA 互连的挑战

SSI 技术解决了以前阻碍将两个或更多 FPGA 的互连逻辑结合起来以创建一个更大的 "虚拟 FPGA "来实现复杂设计的难题。这些挑战包括:

可用的 I/O 数量不足以连接分区设计中 FPGA 之间必须传递的复杂信号网络,也不足以连接 FPGA 与系统的其他部分 FPGA 之间信号传递的延迟限制了性能 使用标准设备 I/O 在多个 FPGA 之间建立逻辑连接会增加功耗。

主要挑战连接有限

SoC设计由数百万个门组成,这些门通过多总线形式的复杂导线网络、复杂的时钟分配网络和大量控制信号连接起来。要在多个 FPGA 之间成功分割 SoC 设计,需要大量的 I/O 来实现跨越 FPGA 之间的网络。由于SoC设计包括宽达 1024 位的总线,即使采用最高引脚数的 FPGA 封装,工程师也必须使用数据缓冲和其他设计优化方法,而这些方法在实现高性能总线和其他关键路径所需的数千个一对一连接时效率较低。

封装技术是造成 I/O 限制的关键因素之一。目前,最先进的封装可提供约 1200个 I/O 引脚,远远低于所需的 I/O 总数量。在芯片级,I/O 技术还存在另一个限制,因为 I/O 资源与互连逻辑资源在每个新工艺节点上的扩展速度不同。与用于构建 FPGA 核心可编程逻辑资源的晶体管相比,构成器件 I/O 结构的晶体管必须大得多,才能提供芯片到芯片 I/O 标准所需的电流和耐压。因此,增加芯片上的标准 I/O 数量并不是为组合多个FPGA 芯片提供连接的可行解决方案。

主要挑战:延迟过长

延迟增加是多 FPGA 方法面临的另一个挑战。标准器件 I/O 带来的引脚到引脚延迟会降低跨多个 FPGA 设计的整体电路性能。此外,在标准 I/O 上使用时域多路复用 (TDM) 技术,通过在每个 I/O 上运行多个信号来增加虚拟引脚数,会带来更大的延迟,从而使 I/O 速度降低 4-32 倍或更多。对于 ASIC 原型开发和仿真而言,这些降低的速度通常是可以接受的,但对于最终产品应用而言,速度往往太慢。

关键挑战:功率

TDM 方法也会导致更高的功耗。当在多个 FPGA 之间的 PCB 线路上驱动数百个封装到封装的连接时,标准器件 I/O 引脚的功耗比连接单片芯片上的逻辑网更高。同样,多芯片模块(MCM)技术为在单个封装中集成多个 FPGA 芯片提供了减少外形尺寸的潜在优势。然而,MCM 方法仍然受到 I/O 数量有限以及不理想的延迟和功耗特性的限制。

关键挑战:高速串行连接的信号完整性

特别是在通信应用中,高速串行 I/O 连接非常普遍,信号完整性差可能成为阻碍设计完成的主要瓶颈。FPGA 必须提供适当的收发器信号保真度,否则就必须花费无数的时间来完善 I/O 参数、修改 PCB 设计和进行通道优化,以实现设计的成功。某些应用要求线路速率超过 25 Gb/s,因此提供适当的信号完整性并非易事。

Xilinx SSI 技术

为了克服这些限制,Xilinx开发了一种新方法,用于大批量生产大容量高性能FPGA。新解决方案通过提供数量更多的连接,实现了多芯片之间的高带宽连接。与多 FPGA 或 MCM 方法相比,它的延迟时间更短,功耗更低,同时可在单个封装内集成大量互连逻辑、收发器和片上资源。在 FPGA 系列的密度范围内,中等密度器件代表着 "甜蜜点"。也就是说,与上一代产品相比,中密度器件的容量和带宽要大得多,而其芯片尺寸在 FPGA产品生命周期中的交付时间要早于同系列中的最大器件。因此,通过在单个器件中组合多个这样的芯片,就可以达到或超过最大单片器件所提供的容量和带宽,同时还具有较小芯片在制造和量产时间方面的优势。

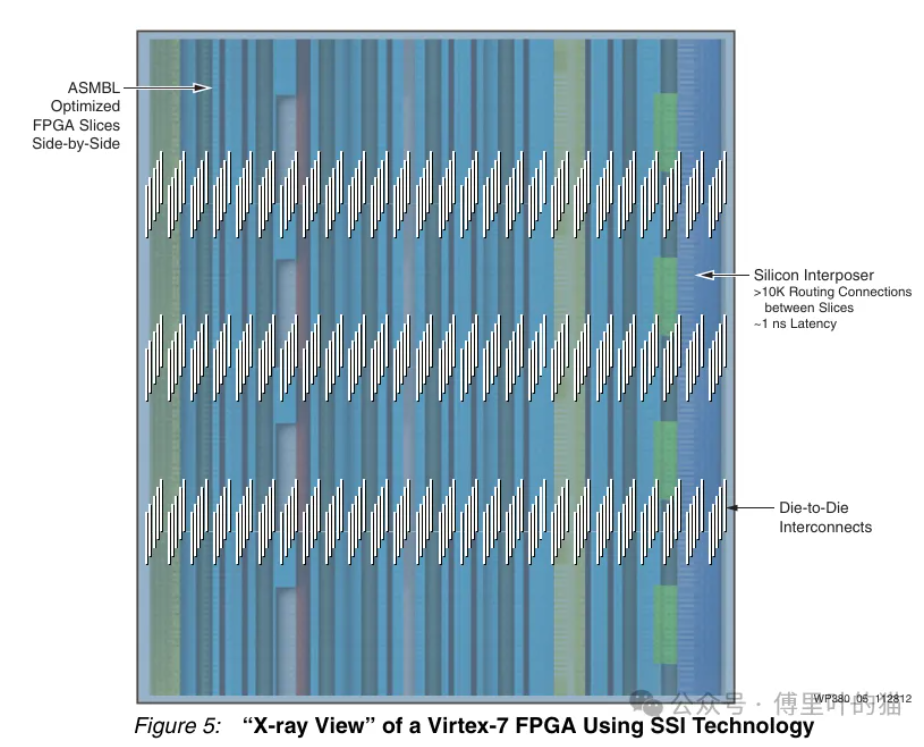

Xilinx以创新的方式应用了多项成熟技术,从而找到了这样一种解决方案。通过将 TSV 和微凸块技术与其创新的 ASMBLTM 架构相结合,Xilinx正在构建一类全新的 FPGA,以提供满足可编程需求所需的容量、性能、功能和功耗特性。Xilinx SSI 技术通过无源内插器将多个 FPGA SLR 结合在一起。内插器可提供数以万计的芯片到芯片连接,从而实现超高的互连带宽,同时功耗更低,延迟时间仅为标准 I/O 的五分之一。下图显示了带有四个 FPGA SLR、硅内插层和封装基板的芯片堆叠侧视图。

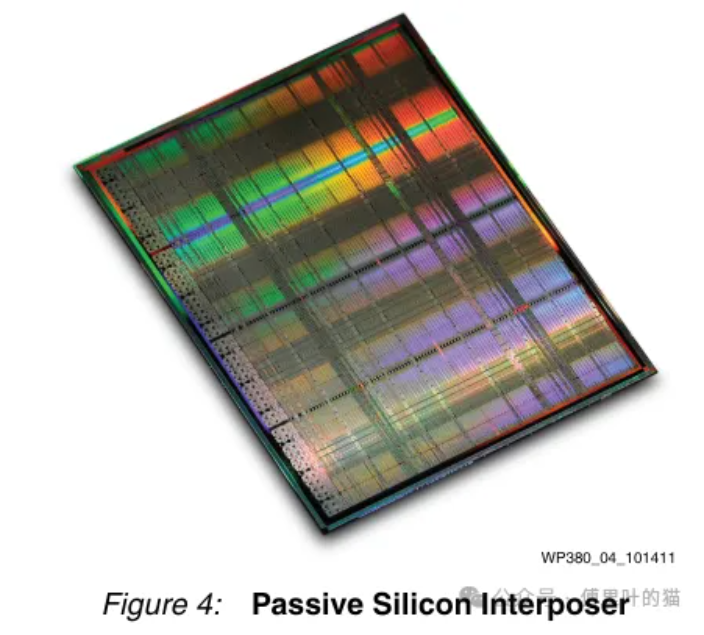

硅内插器最初是为各种芯片堆叠设计方法而开发的,具有模块化设计灵活性和高性能集成度,适用于各种应用。硅内插器是一种基于硅制造工艺(如 65 纳米或 45 纳米工艺)的互连工具,可将多个芯片并排设置并互连。SSI 技术避免了将多个 FPGA 芯片堆叠在一起或堆叠在 MCM 上可能产生的功耗和可靠性问题。与有机或陶瓷基板相比,它们通常硅内插件可提供更精细的互连几何结构(约 20 倍的密集线间距),从而提供器件级互连层次,实现 10,000 多个芯片到芯片的连接。

利用微凸块创建 FPGA 芯片切片,实现堆叠硅集成

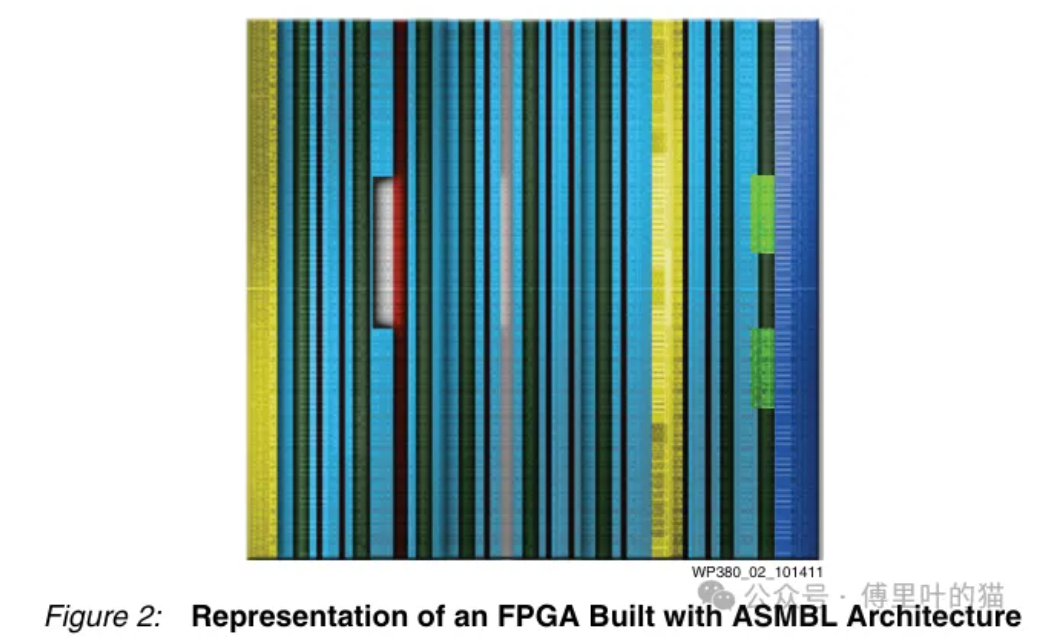

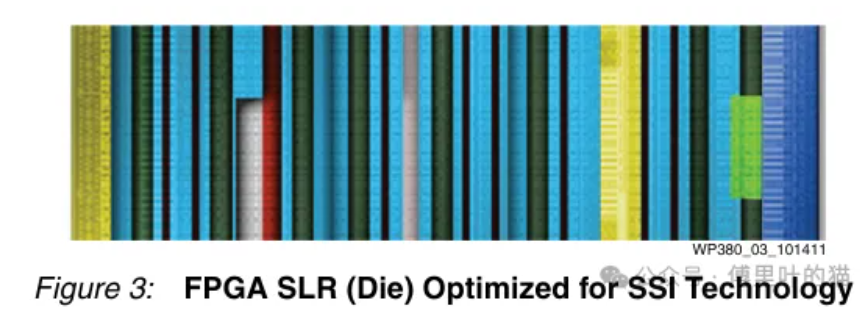

Xilinx SSI 技术的基础是公司专有的 ASMBL 架构,该架构是一种模块化结构,由 Xilinx FPGA 构建模块组成,以Tile的形式实现可配置逻辑块 (CLB)、块RAM、DSP 片、SelectIOTM 接口和Serdes等关键功能。这些资源被组织成列,然后组合成 FPGA。通过改变列的高度和排列,可以创建各种器件来满足不同的市场需求。FPGA 包含用于产生时钟信号和对SRAM 单元进行编程的附加模块,SRAM 单元采用位流数据对器件进行配置,以实现最终用户所需的功能。

带 TSV 的硅集成电路

无源硅内插器将多个 FPGA SLR 互联在一起。它采用低风险、高产出的 65 纳米工艺制造,提供四层金属化层,用于构建连接多个 FPGA 芯片逻辑区域的数万条迹线(图 4)。

SSI 技术可通过超过 10000 个器件级连接提供每秒数太比特的芯片到芯片带宽,足以满足最复杂的多芯片设计的需要。

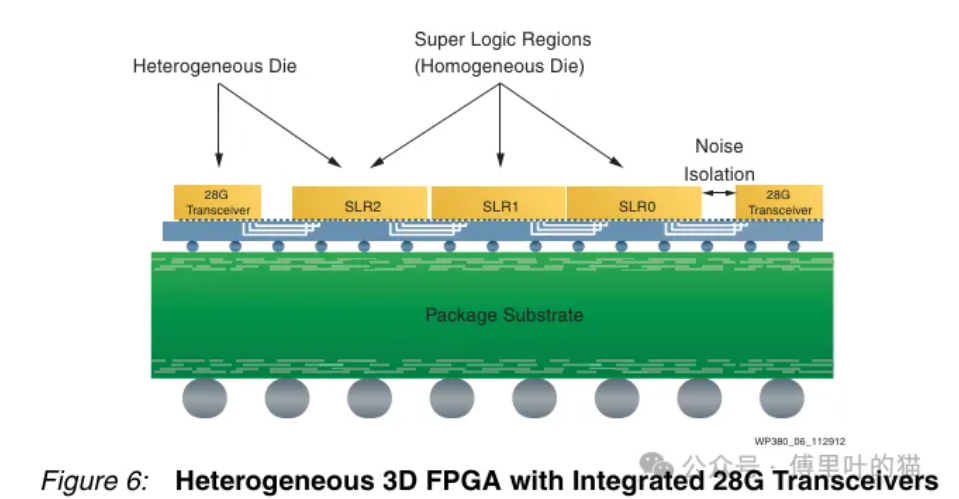

采用异质芯片的 SSI 技术

除了将同质 SLR 集成到硅内插件上,SSI 技术还可以集成不同类型的芯片。在图 6 中,Virtex-7 H870T FPGA 通过硅内插器将三个 SLR 和独立的 28G 收发器电路连接在一起。由于 SLR 和 28 Gb/s 收发器电路代表了不同的硅工艺和功能,Virtex-7 HT FPGA 成为世界上首个异构架构--由异构裸片组成的 FPGA。并排安装,作为一个集成设备运行。

将数字 FPGA 与收发器物理隔离的主要好处之一是噪声隔离。这可确保尽可能低的抖动和噪声,从而简化设计闭合并降低电路板成本。将 28G 收发器与 SLR 分离是异构架构如何为特定应用实现最佳效果的一个例子。由于收发器是复杂的模拟电路,在单片设备上实现它们需要更复杂的设计方法。28G 电路作为一个独立的片,可在不影响数字逻辑功能的前提下,实现尽可能大的容量、最佳的性能和功耗。异构架构的另一个优势是能够提供不同比例的收发器和传统 FPGA 资源。Virtex-7 HT FPGA 拥有多达 16 个 28G 收发器,实现了前所未有的集成,走在了高带宽设计的前沿。