作者:Luke Liu 来源:FPGA FAE技术分享选集

来认识一下AIE吧!

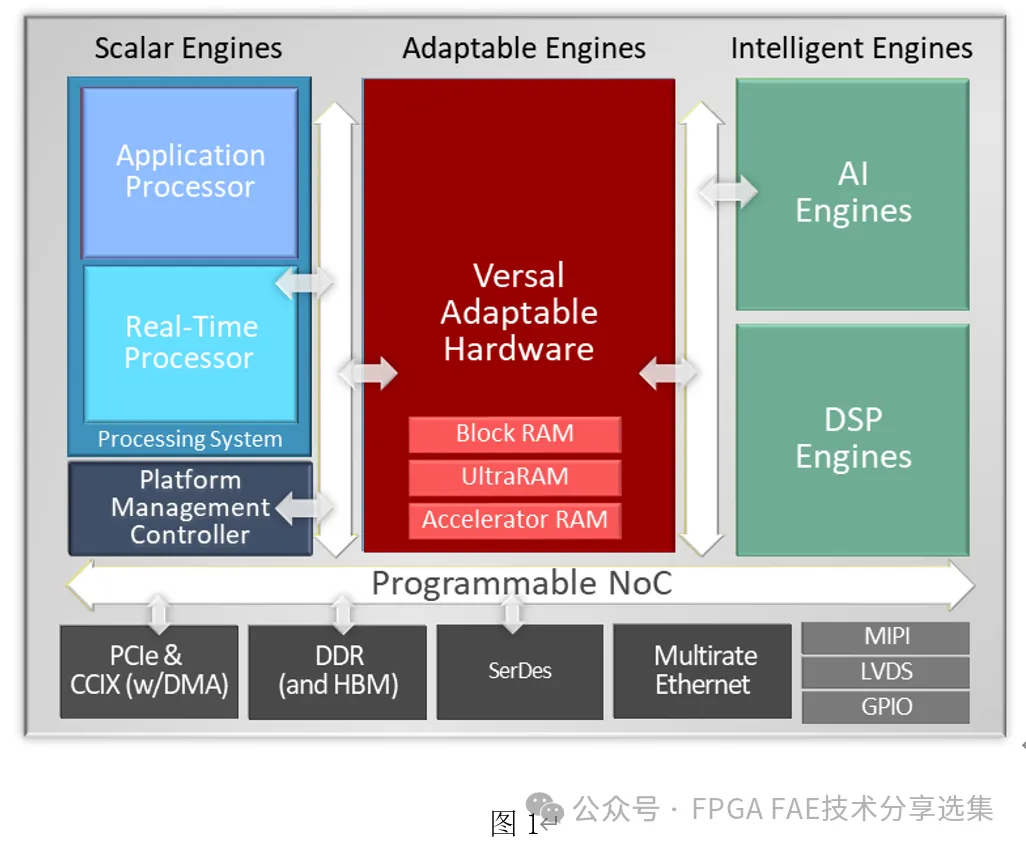

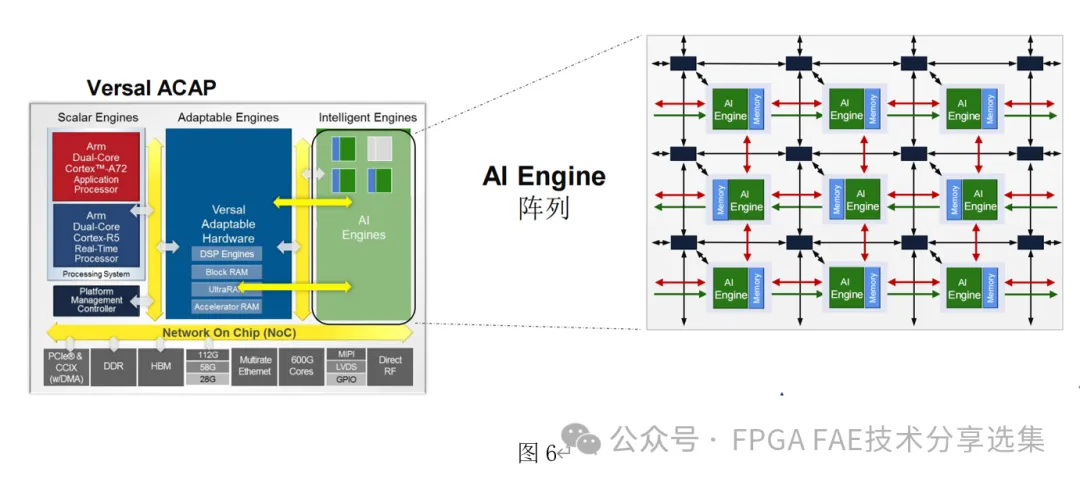

基于ACAP架构的Versal系列产品,在各种加速应用中,相信各位都有所了解了,作为一个异构混合加速平台,Versal结合处理器部分(A72+R5处理器),引以为豪的可编程逻辑\混合了AI Engine(下文简称AIE)和DSP Engine,以及PCIe\高速网络\DDR\高速收发器的连接性能,配合高速片上网络(NoC), 达到了令人期待的加速应用性能:

而AIE(AI Engine)是AMD系列Versal器件的核心模组,凭借其1GHz以上频率的超长指令集\32bit RSIC核心 ,同时支持定点/浮点运算等特性,已经获得了市场的肯定。

而在我们详细介绍AIE之前,我们不妨把视线放回十多年前,看看AIE究竟是怎样的技术演进,为什么在新一代的产品中会成为新一代AMD可编程逻辑器件的标准配置呢?

从GEMM 到 AIE

其实从前面可以看到,AIE和DSP共同组成了”智能引擎”(Intelligent Engines),这种组合不仅仅可以应对人工智能(AI)方面的需求,对传统的无线通信(如波束成型)\信号处理\雷达处理等等,均有很好的表现。而对于AI的应用,当然是AIE的主要场景之一。

实际上,从2005年左右,人工智能的实用化落地刚刚起步,当时的Xilinx就注意到了相关应用,尤其是AI应用传统算法之一,卷积神经网络(CNN)的相关加速。而CNN的加速中,需求比例最大的就是高并行度的矩阵乘(用于卷积)。

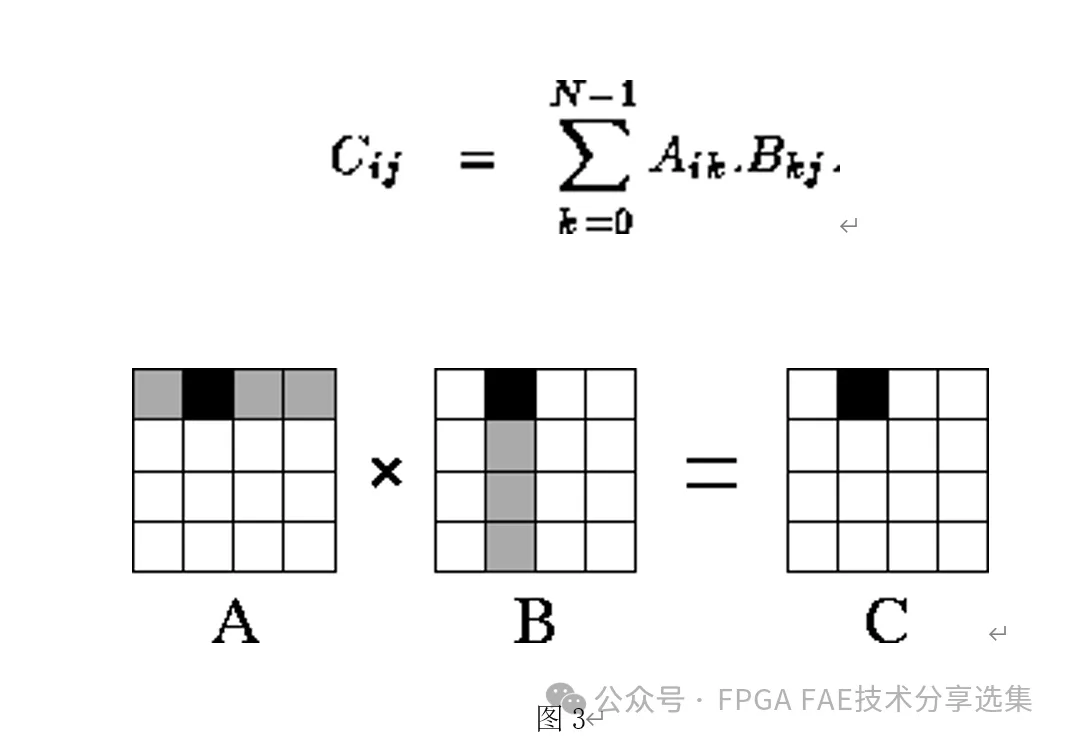

说到矩阵乘,各位对线性代数有所了解的读者,您应该都很熟悉了,其原理简单来说,就是两个矩阵A,B,当AxB时,每一个位置上的结果都是 A矩阵的对应行与B矩阵的对应列的乘累加:

关于矩阵乘的优化算法,本文不再多赘述了,这里给出几篇参考文献:

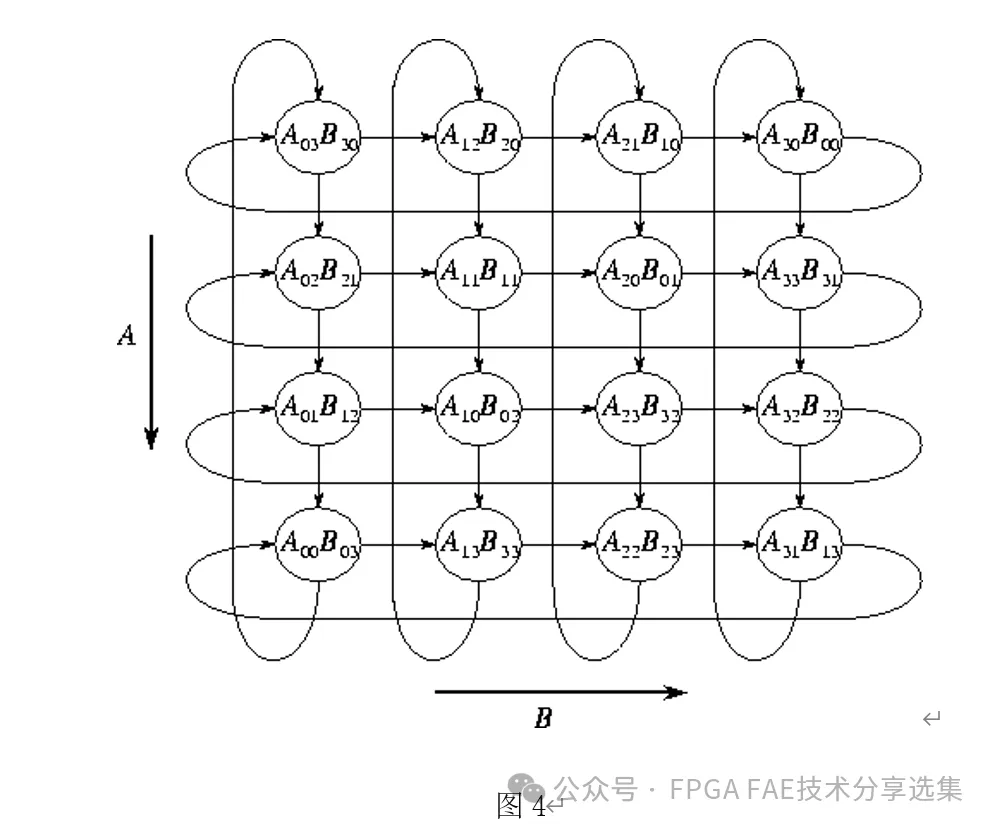

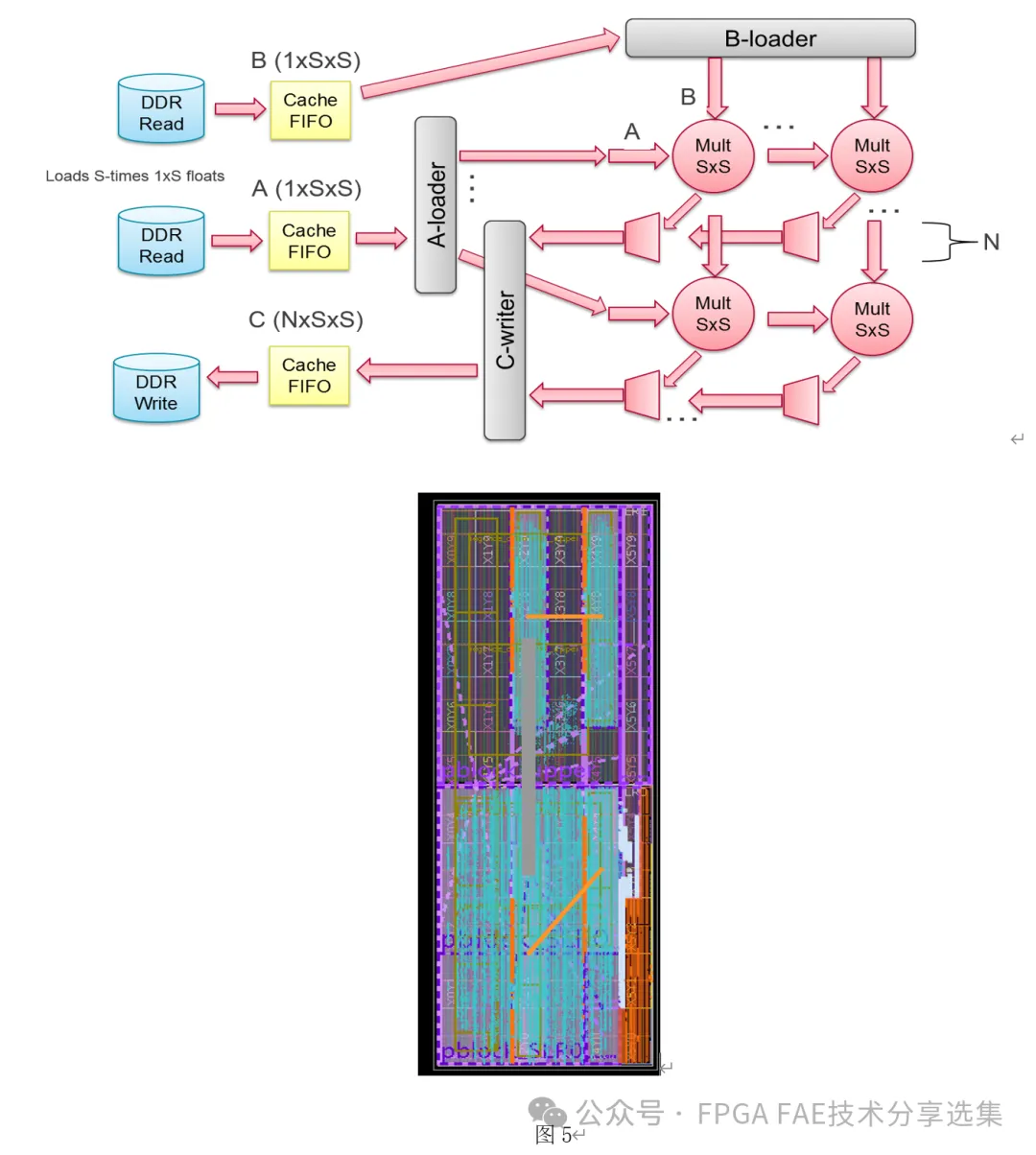

在没有专用AIE的情况下,Xilinx团队提供了名为GEMM(通用矩阵乘,General Matrix Multiplication)的方案,利用20nm器件的DSP,片上RAM,通用逻辑和DDR接口IP,在KU115上实现了时序约束300MHz, 1.228TOPs的加速设计:

有经验的读者大体可以看出来,虽然GEMM已经是很优化的设计了(在20nm器件上实现了300MHz的大设计约束),仍然面临着相关挑战:

有经验的读者大体可以看出来,虽然GEMM已经是很优化的设计了(在20nm器件上实现了300MHz的大设计约束),仍然面临着相关挑战:

1.DSP和加载A\B矩阵数据的RAM靠器件内部导线连接,想约束较高的速度需要靠门槛很高的物理约束,一旦RAM和DSP距离较远(比如跨越了资源Column), 导线长度就会直接限制工具编译约束的速度上限。

从AIE到AIE-ML

从GEMM反观AIE,就可以很好地理解AIE的优势了:

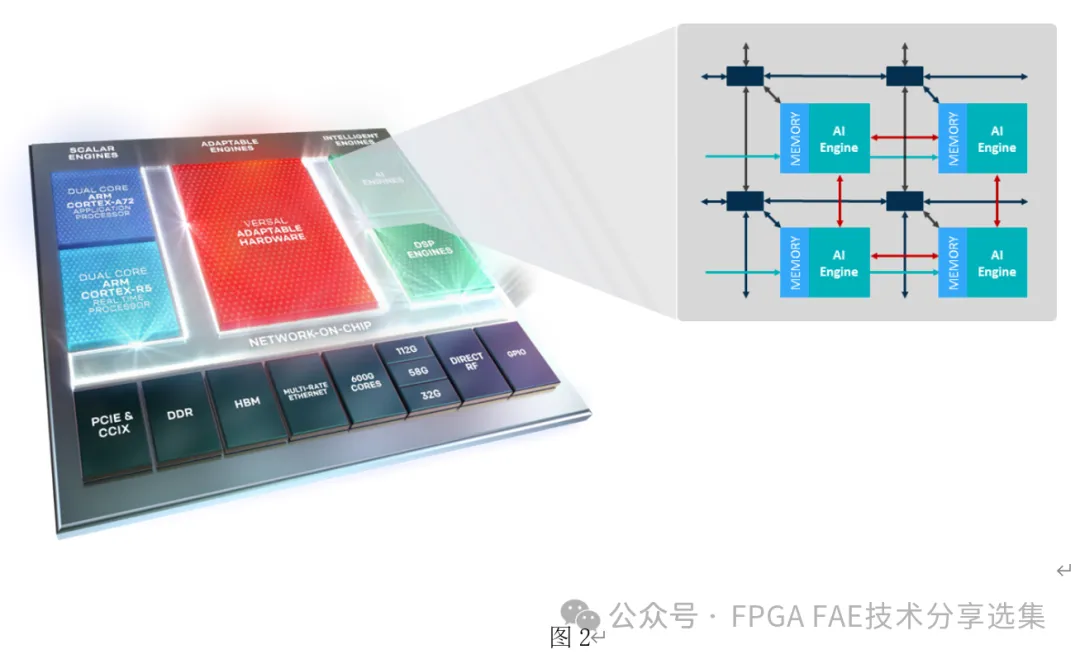

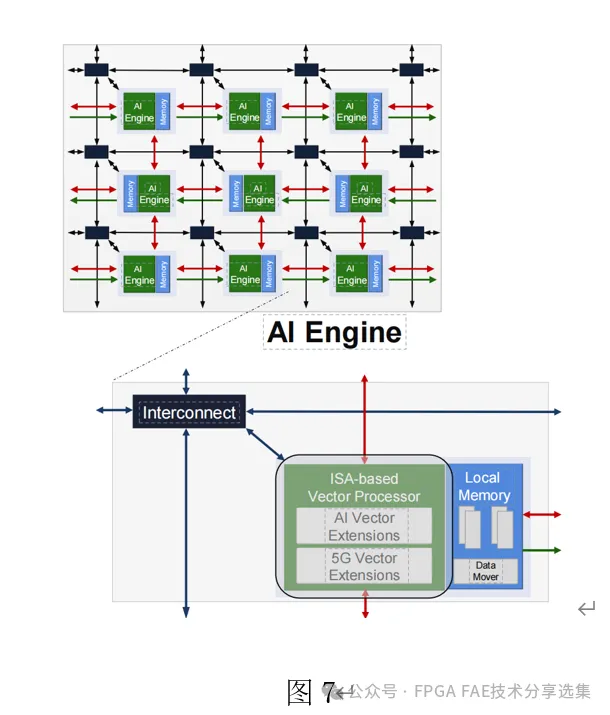

首先,如下图可见,固化实现的AI Engine和物理上一体化的Memory使计算核心可以最高以1.3G的速度读写数据并处理。

其次,阵列的各个AIE之间均有上下左右的连接,对于矩阵相关运算有天然的适配。对于不相邻的AIE单元,也有专门的(如图中黑线所示)的高速互联(Interconnect)。

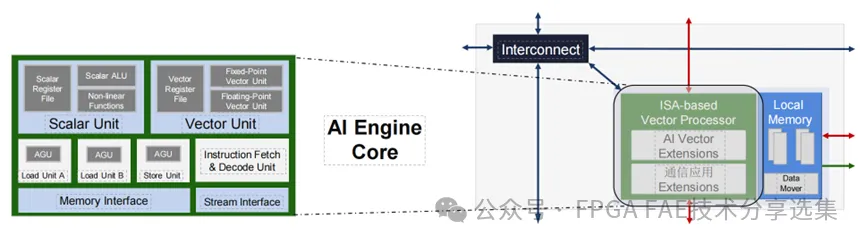

在AIE中,同时提供了AI 指令扩展和通信相关指令扩展,方便应对各种应用:

并支持包括浮点运算和定点运算指令集的向量处理器(Vector Processor),以及其他各DSP相关指令集和存储器界面:

如果我们再回头看GEMM方案,既可以看到AMD可编程逻辑器件的技术演进,更可以看到AIE很好地解决了之前的技术痛点,为拥抱近年来各式新应用打下了坚实的基础。

随着为了适应AI的发展,Versal的后续版本也引入了AIE-ML,相对于第一版AIE,通过加强向量处理器中的AI指令集,将每个向量处理器侧的片上存储器从32KB增加到64KB,对大尺寸的矩阵运算有更好的支持。

AIE,到更远的未来

从Versal 系列产品中可以看出,基于ACAP(自适应计算加速平台)架构的异构处理器件,AIE能展现的性能取决于整体芯片的架构和计算效能。随着Versal系列产品的持续发展,包括PCIe5 \DDR5\更高级更多核的A系列处理器核心和R系列实时处理器等新能都在纷纷加入。在不久的未来,AIE的应用场景会更加广泛,其可实现的性能也在与日俱增。未来已来,敬请持续关注我们!

如果您在AIE方面有疑问,欢迎联系: