作者:张海军,来源:傅里叶的猫

这是一篇翻译自国外的4年前的文章,内容较长,我对原文内容做了精简,干货满满,希望大家可以读完,同时我们可以从现在这个时间点回看作者4年前的判断。

大型科技公司投资数十亿美元用于 AI 芯片开发。甚至 Microsoft 和 Meta 也采用了英特尔 FPGA 来加速其硬件基础设施。有少数初创公司已经是独角兽,但也有像 Wave Computing 这样的悲惨故事,它在 3 年内筹集了 1.87 亿美元资金后申请破产。在本篇文章中,我们介绍几家知名公司,包括国际巨头和初创,我们将专注于这些公司的技术领域,重点是确定未来的进步和趋势。

Nvidia GPU

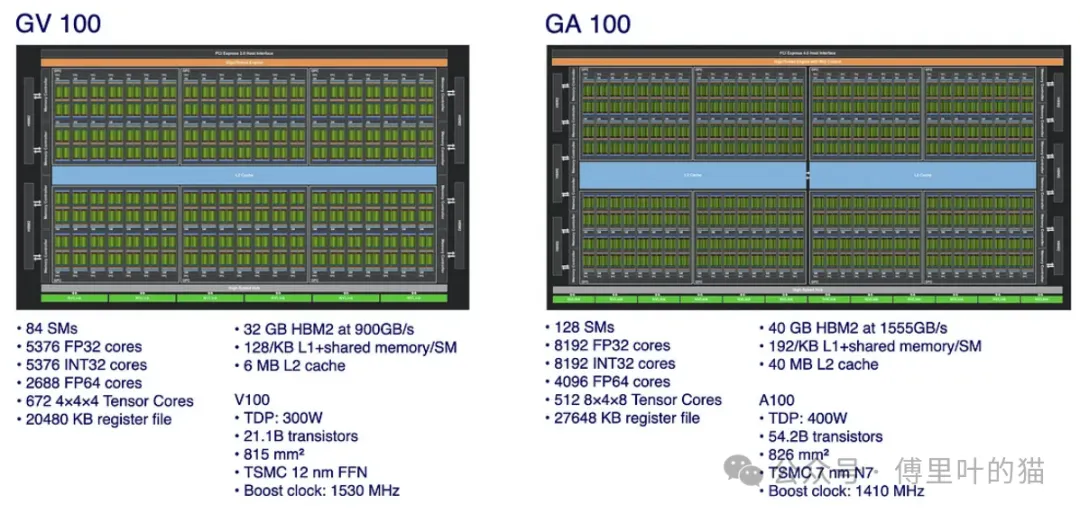

GV100(Volta 架构)于 2017 年底发布,而 GA100(Ampere 架构)于 2020 年发布

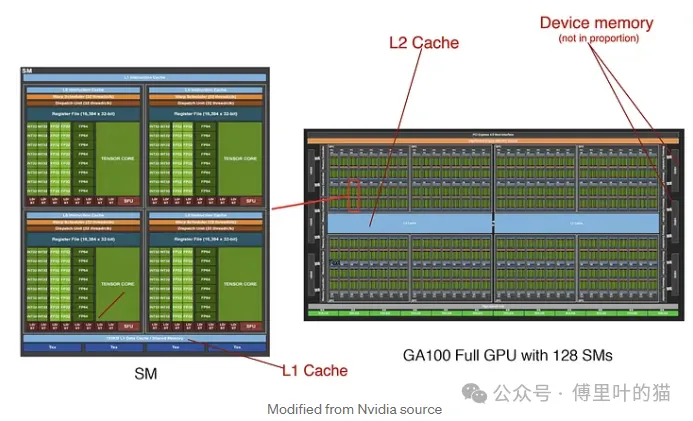

GA 100 GPU 使用台积电 7 nm 制造,而不是 GV 12 中的 100 nm 工艺。虽然它们的芯片尺寸大致相同,但 GA100 中的流式多处理器 (SM) 数量增加了 50%,达到 128 个,FP32 内核的数量从 5376 个增加到 8192 个。新的 Gen3 Tensor Core 执行 8×4×8 矩阵乘法,而不是 4×4 x 4×4。

到目前为止,这些趋势在许多 AI 芯片中都是意料之中的——更多内核具有更好的矩阵乘法单元,适用于深度学习 ,但是有一些明显的设计改进。

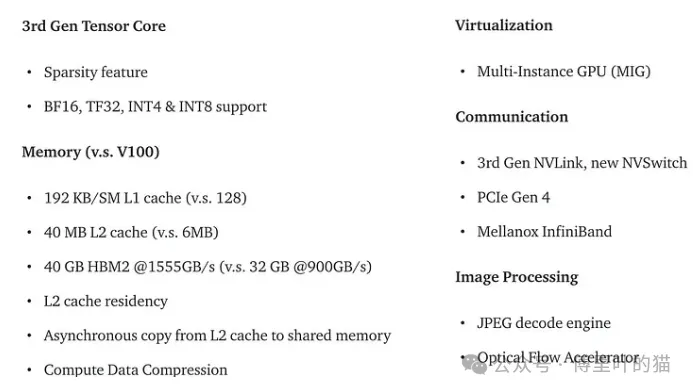

其次,DNN(深度神经网络)权重稀疏性被大量利用。数据压缩后,片外存储器和片上缓存之间传输的数据量显著减少 2 到 4 倍。凭借这种稀疏性, Tensor Core 经过重新设计,可实现更快的操作。

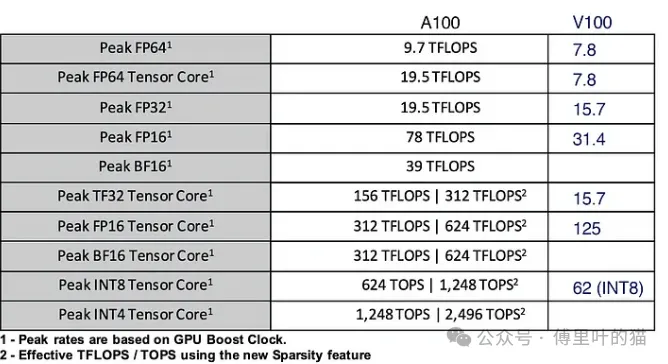

第三,支持更多数据类型(BF16、INT4、TF32)。在 DL 中,总体趋势是 16 位矩阵运算,值范围等于 FP32 用于训练,甚至希望 8 位用于推理。如下所示,对于较低精度的算术,一些改进是一个数量级。

第四,更快的 GPU 间通信,以处理无法放入一个 GPU 的模型训练。

第五,为端到端解决方案创建了新功能,例如视频编码/解码。

此外,NVidia 是最成熟的 AI 芯片提供商。为了处理真正的客户需求,添加了 GPU 虚拟化(MIG 功能将单个 GPU 转换为多个虚拟 GPU),以便在基于云的推理中更好地利用。

作为参考,这些是 A100 GPU 相对于 V100 对特定增强功能所做的性能改进幅度。

Google TPU

通用 GPU 有它本身的劣势,具体来说,GPU 比 ASIC(专用集成电路)消耗更多的能量,并且具有更高的延迟。

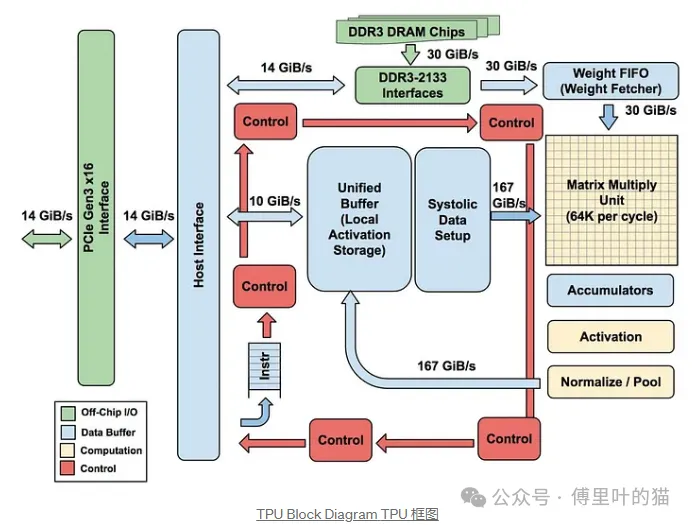

芯片公司可以设计 ASIC 芯片以实现最高效率,但开发成本昂贵且无法适应变化。自 2012 年 AI 取得突破性成功以来,Google 在缩小这些设计要求方面积累了丰富的经验。事实上,它得出的结论是,Google TPU 只需要高吞吐量进行矩阵乘法、激活、归一化和池化。

这导致了一个非常重要的设计趋势:指令调度、优化和资源分配等工作转移到 CPU 和编译器中的runtime库。

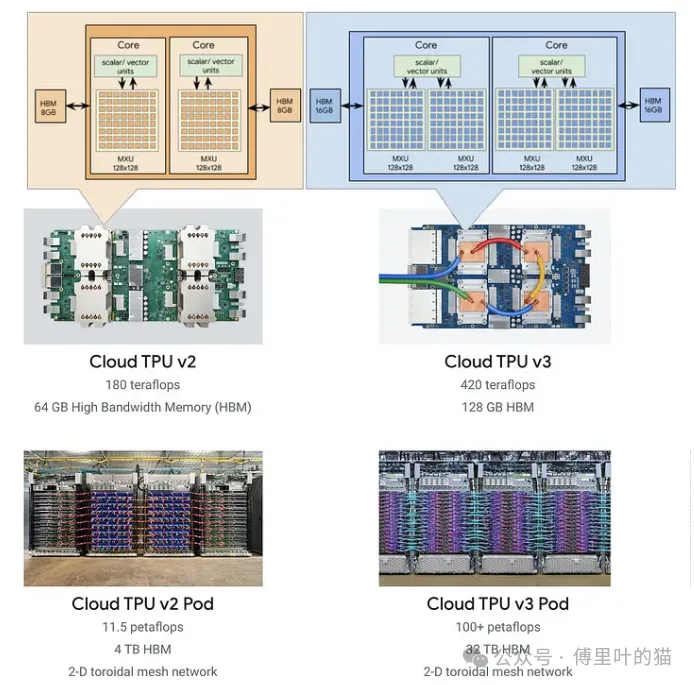

如下图所示,TPU v3 的核心数量是 v2 的两倍,而 TFLOPs 略多一倍。TPU v4 的性能将再次翻倍 (2.7 倍)。其矩阵乘法单元的吞吐量增加了一倍多。目前尚不清楚太多其他内容,但如果内核数量增加一倍或矩阵乘法大小增加,也就不足为奇了。还提到了互连技术在增加内存带宽方面的未具体进展。这加剧了许多设计人员在推动更高的 TOP 时面临的内存限制。

Google 拥有构建垂直解决方案的资金资源、权力和意愿,他们自己的数据中心和云服务已经为 TPU 提供了成熟的市场。保持专注,简化设计,并优化重要的事情似乎是 TPU 的重点。

Intel FPGA

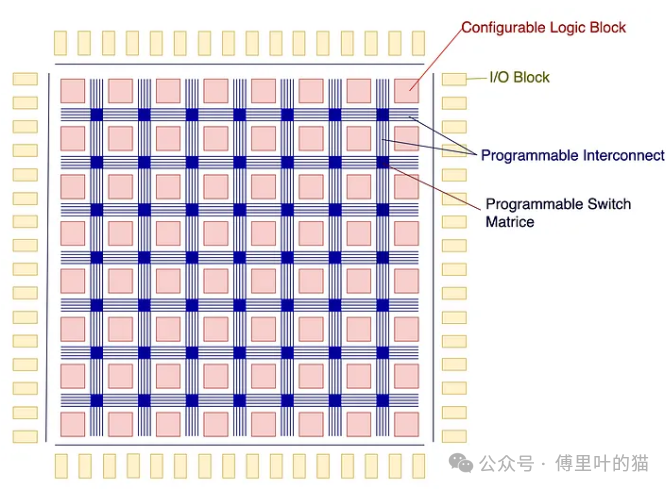

然而,ASIC 的僵化困扰着 Meta或 Microsoft 等公司。为了在设计和选项方面具有更好的灵活性,他们正在研究 FPGA 等解决方案。GPU 和 TPU 的硬件设计无法更改。但几十年来,FPGA 一直允许硬件设计人员进行可重新配置的 ASIC 设计,可以在 ∼20ms 内重新编程。

软件工程师对 FPGA 不太熟悉,那么,让我们做一个简单的概述。FPGA 包含用于 logic 和 arithmetic 函数的 blocks 数组。FPGA 在每个 block中创建自定义函数时,对其可重构性提出了许多想法。此外,这些模块可以通过可编程互连进行连接,以构建具有特定并发性、延迟、I/O 吞吐量和功耗的自定义功能。

Microsoft Project Brainwave 使用 Intel Stratix 10 FPGA 来加速必应智能搜索功能和 Azure 等服务中的 DNN 推理。提供其他英特尔 FPGA 产品线,包括面向不同细分市场的 Agilex(高端)和 Arria。

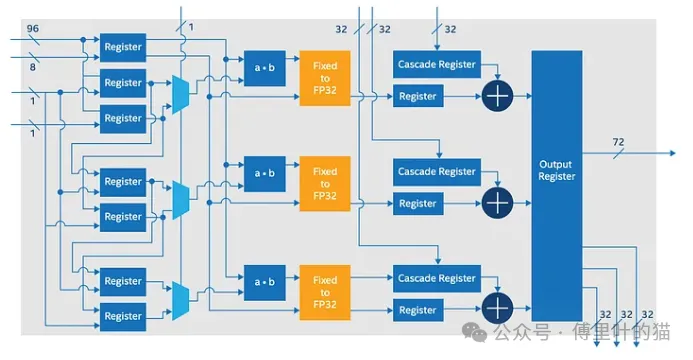

与 GPU 一样,FPGA 最初是为不同的市场设计的。FPGA 在构建自定义功能时提供块之间的细粒度连接。但在某些上下文中,这对 AI 芯片来说是冗余的,负责互连的细粒度连接显著增加了芯片尺寸。它还会增加延迟和功耗。AI 芯片需要与更复杂的块进行粗粒度连接。为了满足这些需求,创建了专门的 AI IP 块。例如,Intel Stratix 10 NX FPGA 是专门使用 AI Tensor Blocks 设计的。这些模块包含密集的低精度乘法器数组,这些乘法器针对使用 INT4、INT8、Block FP12 或 Block FP16 运算的矩阵和向量乘法进行了优化。此外,这些张量块可以级联在一起以支持大型矩阵。

然而,AI 模型和 FPGA 编程之间存在巨大差距,后者谈到了时钟和信号。在 FPGA 中,设计人员使用 HDL (Hardware Description Language) 来描述硬件设计,然后将其编译成 bitstreams 以重新配置芯片。在 AI 领域,FPGA 供应商在专门用于优化每个 DL 模型(如 ResNet、GoogleNet 等)的比特流上投入了大量资金。

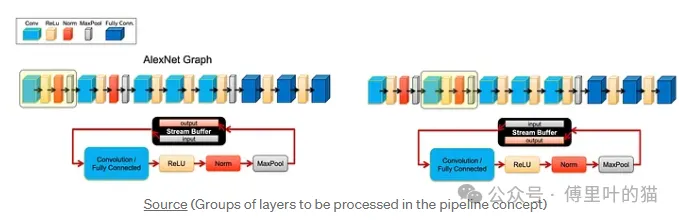

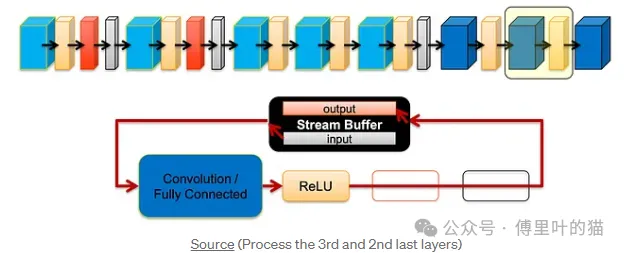

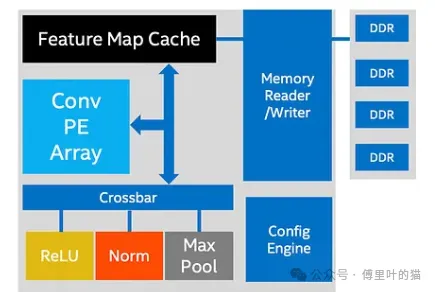

在这些比特流中,DNN 层被映射到pipeline 中进行处理,类似于 TPU。在下面的演示中,AlexNet 层被分组为包含 CNN 层、ReLU、归一化和最大池的块。每个块都将在pipeline 中执行,并带有一个保存中间计算的流缓冲区。

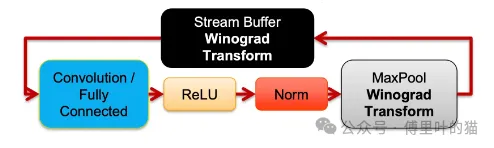

凭借设计自己的硬件的灵活性,它可以实现算法,例如 Winograd Transform 来加速 CNN 卷积。

无需从头开始,FPGA 提供了使用垂直 IP blocks 和专用 bitstreams 来定制新硬件设计的灵活性,旨在实现类似 ASIC 的性能。此外,它可以加速 Microsoft 或 Meta数据中心所需的 ML 算法,而不仅仅是常见的深度学习算法。

Xilinx ACAP

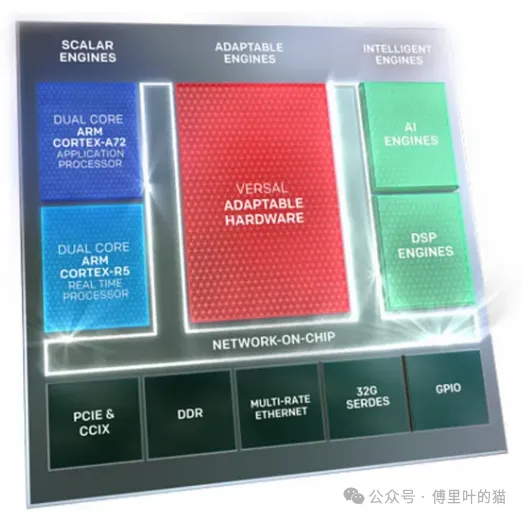

Xilinx Versal 是一个自适应计算加速平台 (ACAP)。ACAP 是一个异构计算平台,结合了标量引擎、自适应引擎(又名可配置逻辑块 CLB)和 AI 引擎。我们可以将其视为 SoC(片上系统)的 AI 版本。所有这些引擎都与片上网络 (NoC) 互连,以实现多TB通信。

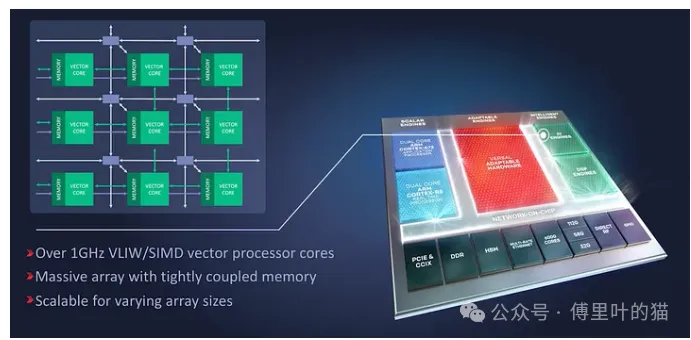

AI 引擎包含一组具有紧密耦合本地内存的 VLIW/SIMD 矢量内核。与 FPGA 一样,它针对专业硬件设计具有高度可配置性,并且针对 DL 推理。

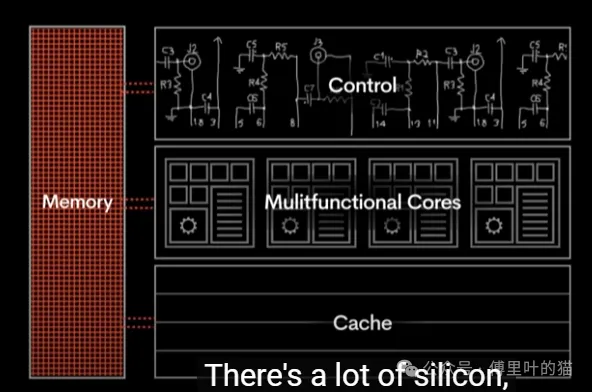

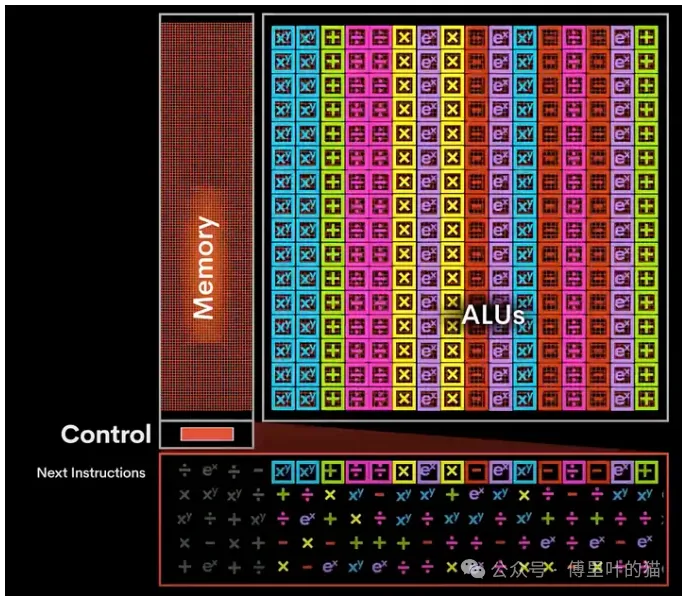

它的pipeline 结构略有不同,pipeline 从左向右移动,其中同一列中的内核执行相同的指令 (SIMD)。TSP 包含一个具有数百个功能单元的处理器。

大部分 control logic 和 cache 都消失了。它在很大程度上取决于编译器和主机发出指令,这大大减少了指令解码开销。

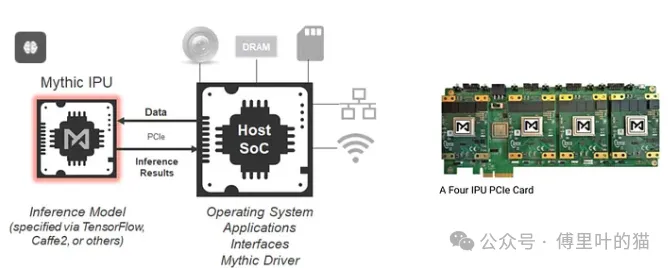

Mythic芯片是基于图块的,具有三种基本硬件技术:

Compute-in-memory Dataflow architecture Analog computing

第一项和第二项就是使用本地化内存和数据流概念来运行 DNN,这算是比较常规的操作:

当一个图形节点的结果完成后,它们将流向下一个图形节点以开始下一个操作,这对于数据流架构来说是理想的。在我们的数据流架构中,我们为每个内存计算数组分配一个图形节点,并将该图形节点的权重数据放入该内存数组中。当该图形节点的输入数据准备就绪时,它会流向与内存数组相邻的正确位置,然后由本地计算和内存执行。

他们的第三项创新非常有趣。它不使用数字电路设计,而是根据权重调整电阻器的值,并使用输入值来控制电压。输出电流将决定计算结果。以下是 Mythic 的详细信息。

我们的模拟计算将内存计算发挥到了极致,我们直接在内存数组本身内部进行计算。这可以通过将存储元件用作可调电阻器、以电压形式提供输入并将输出收集为电流来实现。我们将模拟计算用于核心神经网络矩阵运算,其中我们将输入向量乘以权重矩阵。

首先,它的效率非常高;它消除了神经网络权重的内存移动,因为它们被用作电阻器。其次,它是高性能;当我们执行其中一个向量运算时,会有数十万个乘法累加运算并行发生。