文章来源: OpenFPGA

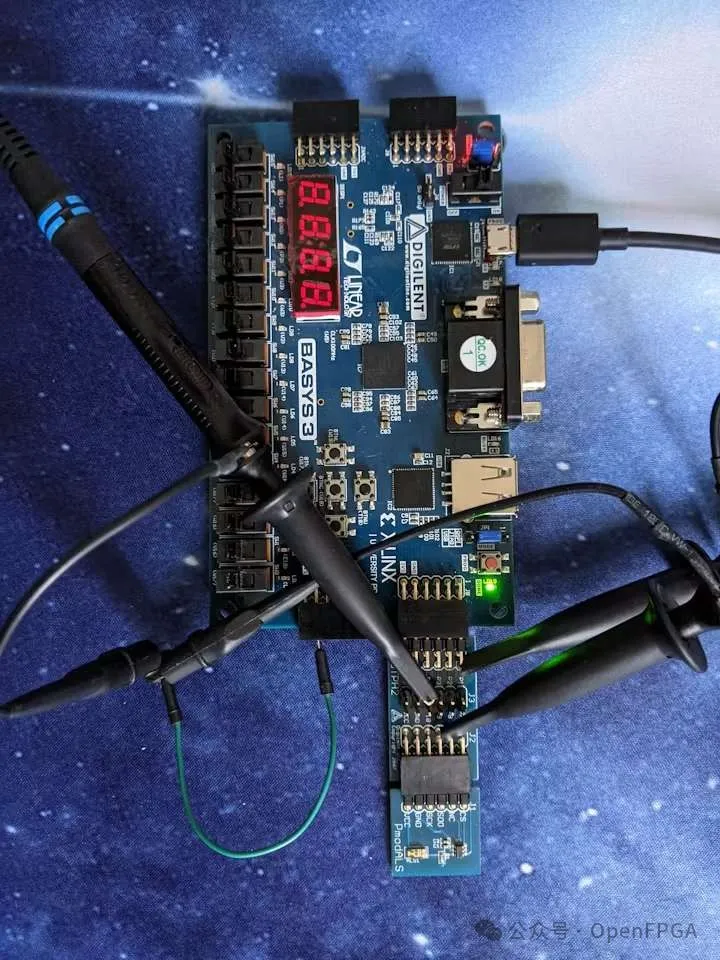

之前介绍过使用RP2040制作逻辑分析仪及示波器,今天我们使用FPGA搭建逻辑分析仪。

目前国内逻辑分析仪主流的架构都是使用FPGA+USB PHY,结合FPGA的优点及USB的高接入性使其一直占据着中高端市场。

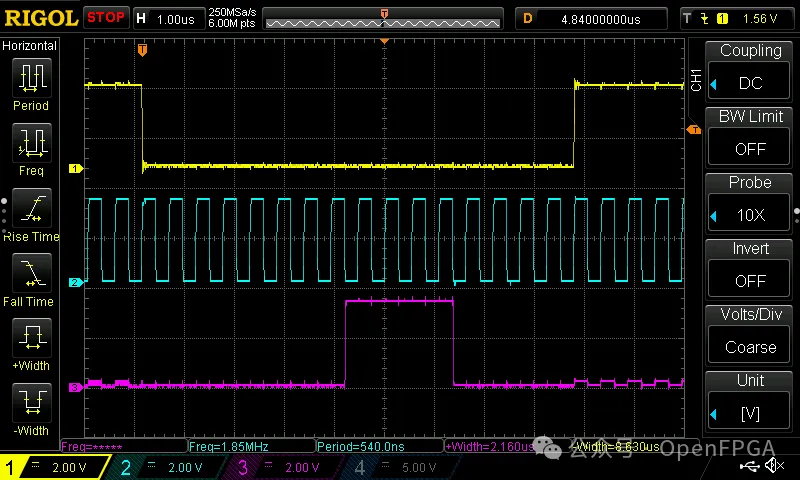

今天就使用FPGA搭建逻辑分析仪,为了通用性,这次和上位机通信选择串口,这样移植性大大增加。

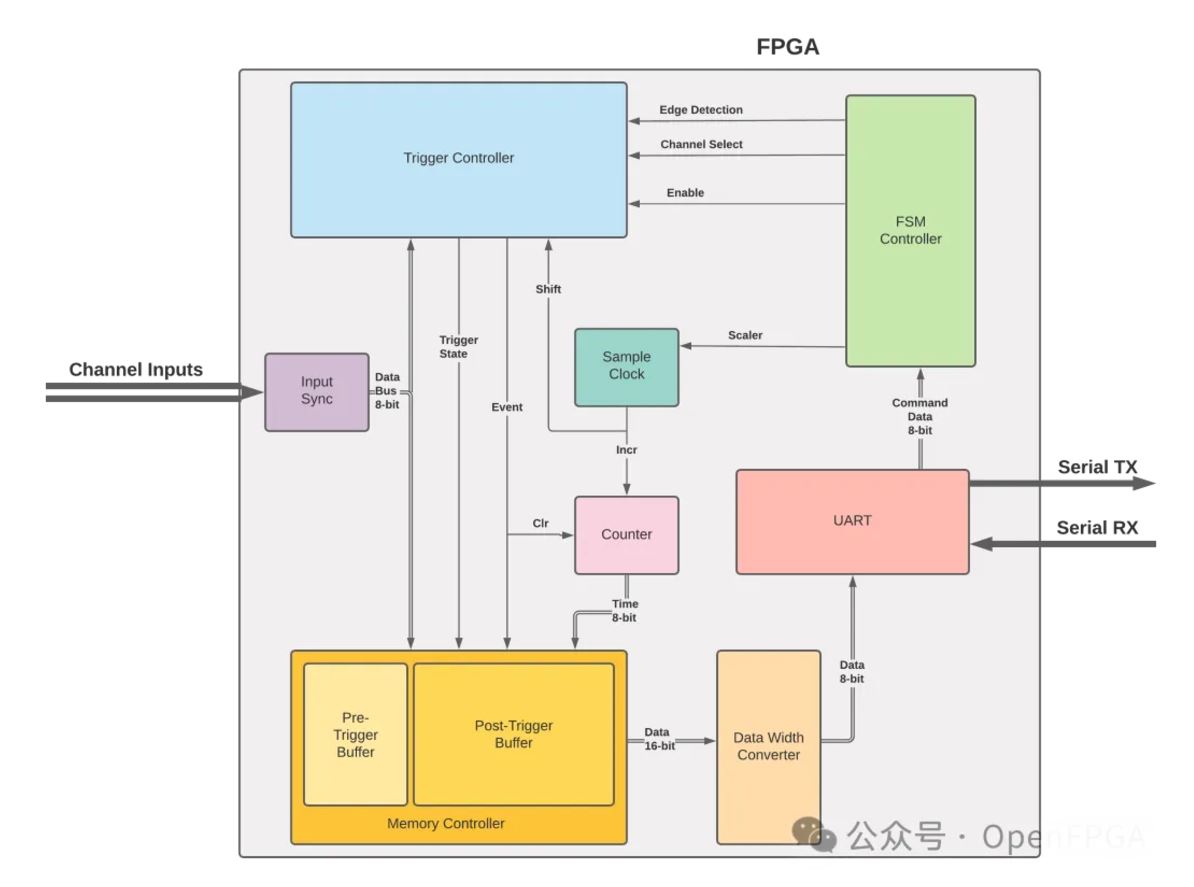

整体架构

该项目由 7 个模块组成,用于实现逻辑分析仪功能:触发控制器、采样率计数器、缓冲区、控制模块和 UART 通信。

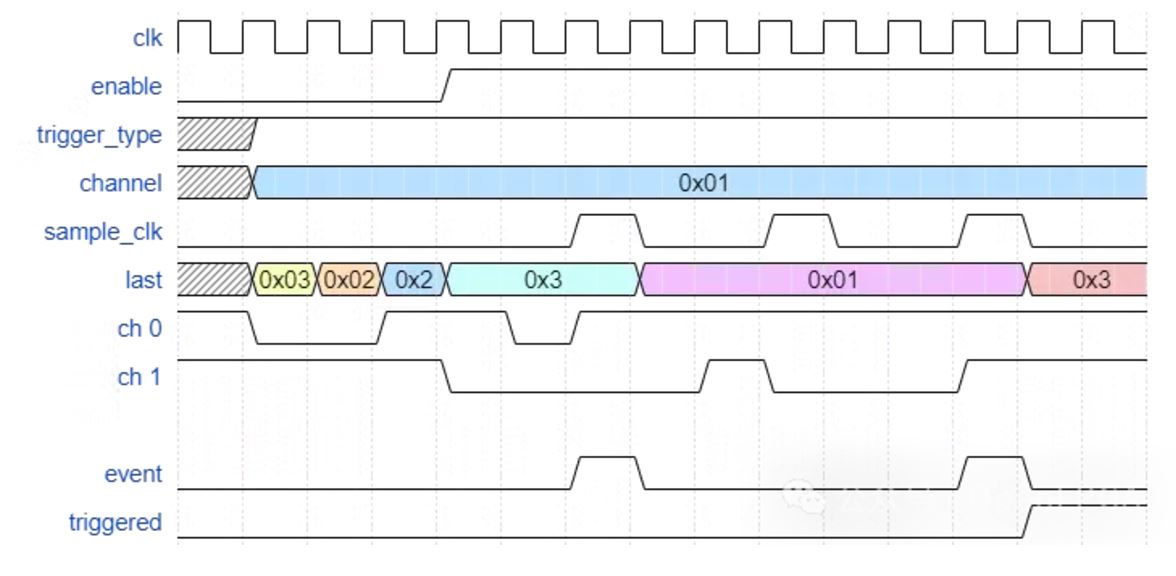

该模块为用户可配置通道上的触发条件。该条件可以通过GUI设置是下降沿或上升沿。采样率信号用于告诉触发控制器何时移入新输入数据。如果新数据与当前数据不匹配,则将向其他模块发送信号。一旦触发条件匹配,就会将触发状态信号发送到缓冲区。

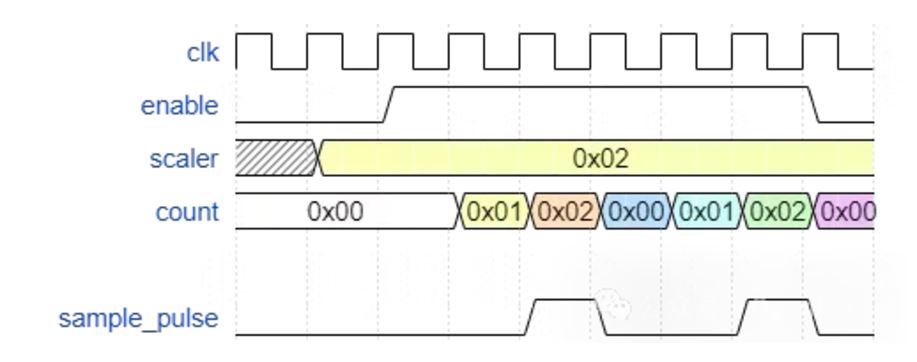

采样率计数器

该系统采用 16 位除数,告知逻辑分析仪采样频率应为多少。采样率信号控制新数据移入触发控制器的频率以及时间戳计数器应递增的频率。在 GUI 中,需要将此除数与 FPGA 时钟频率结合使用,以便从相对时间戳中获取时序信息。

时间戳计数器

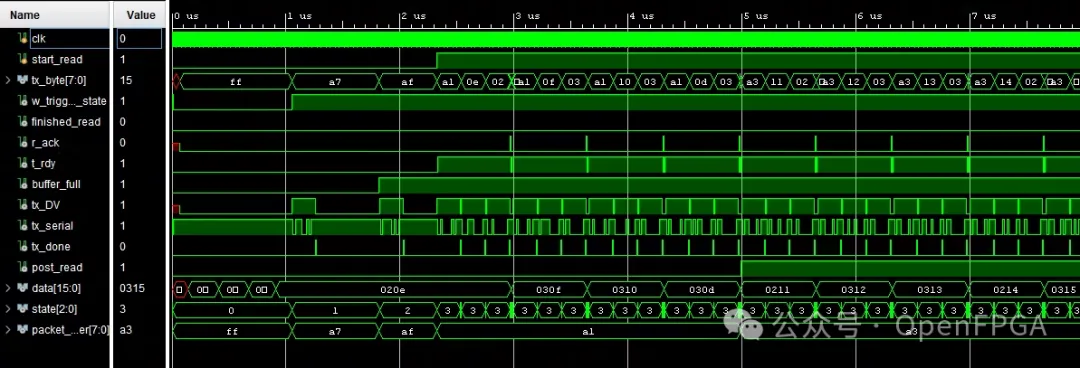

该系统使用一个 8 位寄存器来计算采样时钟脉冲的数量。该寄存器与输入数据连接在一起,然后保存到缓冲区。时间戳计数器在每个采样时钟上递增,跟踪事件之间的相对时间。如果发生事件,计数器将重置为 1 并恢复计数。如果计数器溢出,则会发出信号,让内存控制器在缓冲区中开始新的条目。启用信号用于将计数器保持在 1,直到开始捕获。

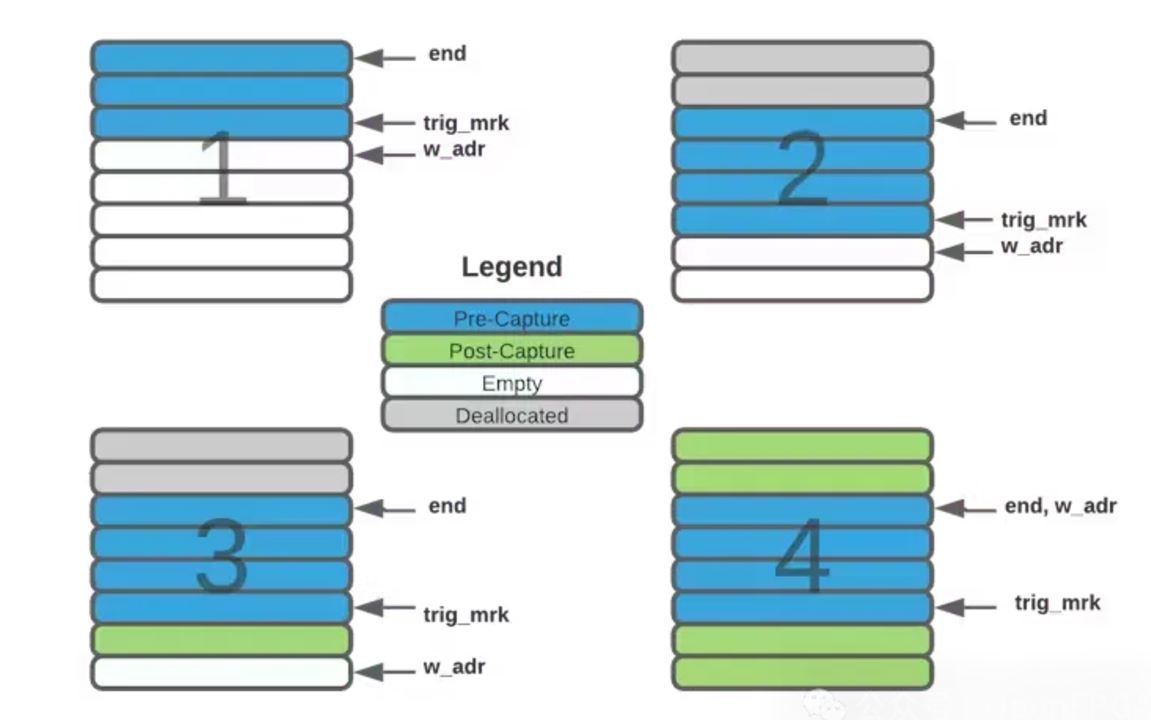

缓冲区

缓冲区将时间戳和数据存储在 RAM 中。每次收到事件或时间戳翻转信号时,缓冲区中的新数据就会开始记录。在触发条件发生之前,此模块充当循环缓冲区,不断覆盖先前的条目。此循环缓冲区的大小可在 GUI 中编程,占整个缓冲区的比例为 10% 到 90%。一旦触发条件发生,缓冲区将充当 FIFO,填满剩余的内存。一旦满了,控制器模块就会收到信号,并逐行读出数据。

UART通信

该模块只是等待主机 PC 发送字节并将命令转发给控制器模块。

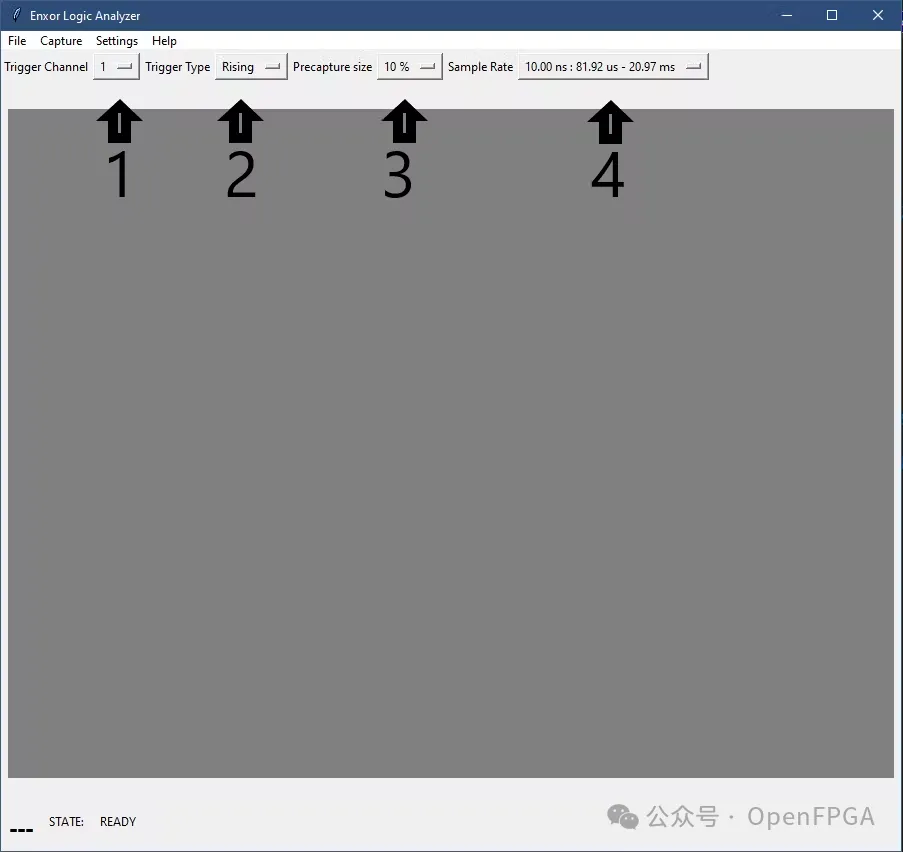

GUI使用

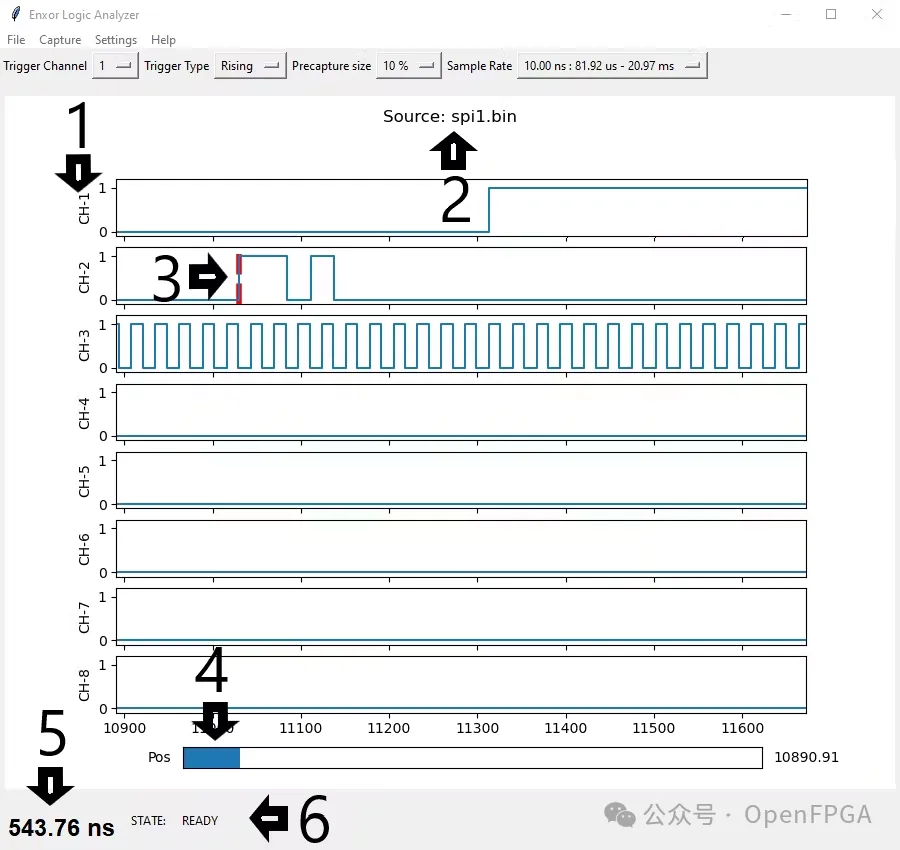

主菜单捕获按钮

1:选择哪个通道来观察触发条件。

2:设置触发类型是上升沿还是下降沿。

3:设置触发事件之前的数据比例。

4:设置采样率,第一个数字表示采样间隔率,接下来的两个数字分别表示最小和最大记录时间。

1:通道名称。

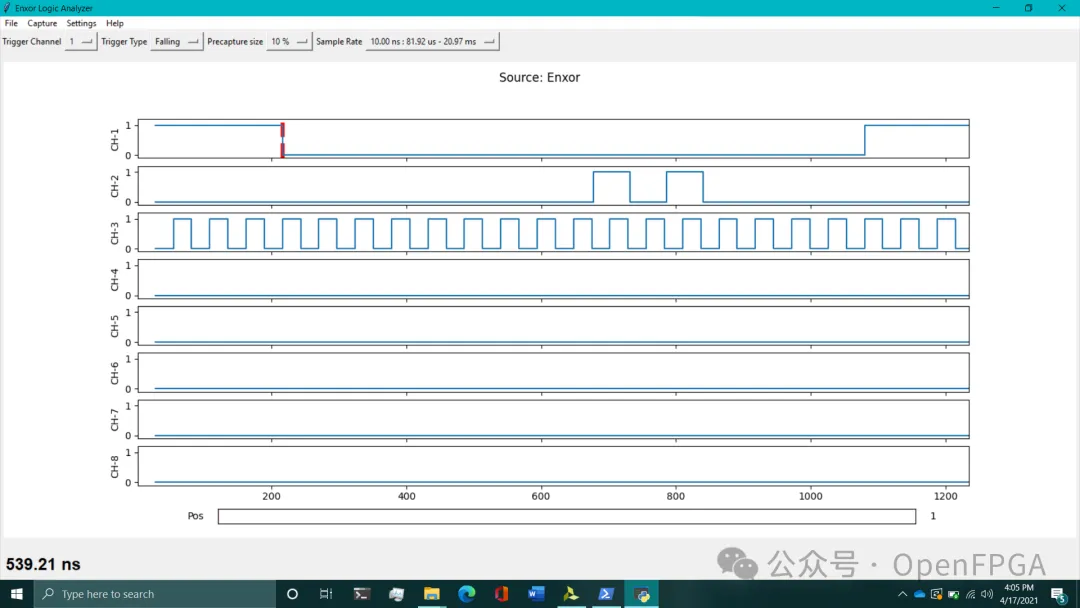

2:表示数据来自哪里。如果从某个文件加载,则设置为文件名;如果数据直接来自逻辑分析仪,则设置为 Enxor。

3:红色条表示触发点发生的位置。

4:位置滑块控制 x 轴。单击并拖动滑块以将其移动到新位置。

5:时间间隔测量。单击波形上的任意位置,然后单击第二个点,可显示两点之间的时间。

6:逻辑分析仪的状态。READY状态表示逻辑分析仪已准备好开始捕获。当逻辑分析仪已启用但尚未触发时,状态将为WAITING。触发事件后,状态将为TRIGGERED。如果中途停止捕获,则状态将为STOPPED。

https://github.com/lekgolo167/enxor-logic-analyzer