文章来源:FPGA技术联盟

1、刷新

SDRAM 内部存储体是利用电容能够保持电荷以及可充放电的特 性制成,而电容所存储的电荷会随时间不断流失,会造成存储数据的丢失。为保证 SDRAM 中数据的可靠性,需要对 SDRAM 进行不断刷新。

从SDRAM的名字(synchronous dynamic random-access memory,同步动态随机存取内存)中的Dynamic也可以看出SDRAM是一种需要刷新的器件。SDRAM 的刷新方式分为自刷新和自动刷新两种,这两种刷新方式,在实现和作用上存在差异。

自动刷新模式是在 SDRAM 的正常操作过程中,保证数据不丢失,自动刷新过 程需要外部时钟的参与,但刷新行地址由内部刷新计数器控制,无需外部写入

自刷新模式则主要用于休眠模式低功耗状态下的数据保存,自刷新过程无需外部时钟参与,与自动刷新相同的是,刷新行地址由内部刷新计算器控制,无需外部写入

两者的操作命令相同,当 CKE信号保持高电平时,写入刷新指令,进入自动刷新模 式;当CKE 信号为低电平时,写入刷新指令,进入自刷新模式。

本系列文章因为后续不涉及SDRAM的休眠模式,所以本文只讲SDRAM的自动刷新操作。接下来,以Mircon公司的SDRAM芯片MT48LC64M4A2的数据手册为例,学习一下SDRAM的自动刷新操作,并进行仿真验证其正确性。

2、自动刷新

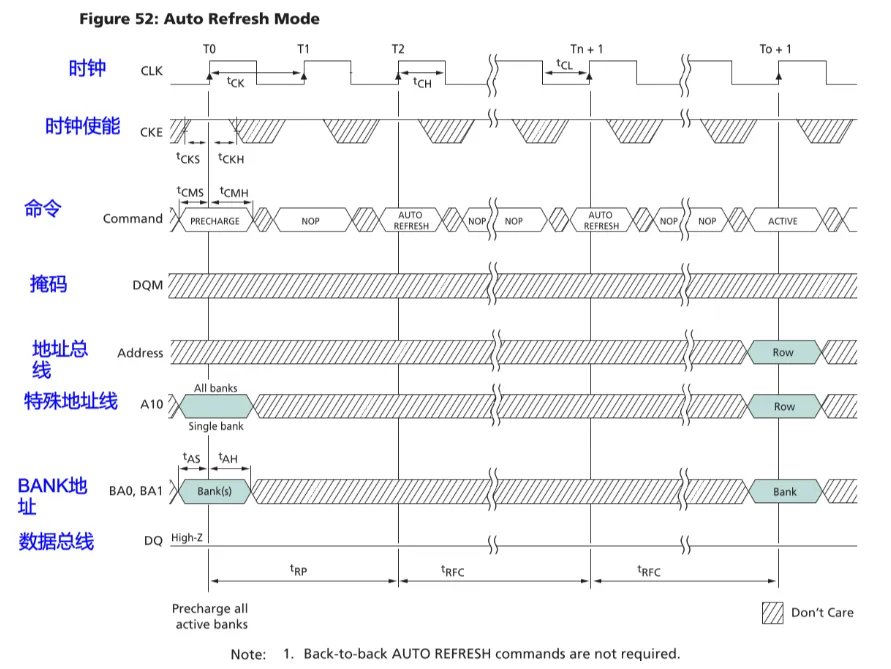

需要注意,SDRAM的所有操作都需要在完成初始化操作后才能进行,自动刷新操作自然也不例外。下图是MT48LC64M4A2的自动刷新时序图:

各信号说明如下:

CK:工作时钟,具体时钟频率视不同的芯片而不同

CKE:时钟使能,在整个初始化过程中都需要拉高

COMMAND:SDRAM命令,由4根线拼接而成,分别是CS#(片选信号),RAS#(行选通信号),CAS#(列选通信号),WE#(写使能信号),通过这4根命令线,再结合SDRAM的地址、输入输出数据等,就可以对SDRAM进行各种命令操作

DQM/DQML,DQMU:数据掩码,通过数据掩码可以实现对输入或输出数据的某一位进行“掩埋”,也就是使某一位失效

A[9:0],A[12:11]:数据地址线,同时也可用来设置模式寄存器

A10:数据地址线,同时也可以用来使能一些具体操作,比如控制自动预充电使能、使能预充电bank数量

BA[1:0]:bank地址

DQ数据:在初始化过程中无数据输出,保持高阻态就行

通过对时序图的分析可以总结出初始化过程如下:

1.对所有BANK进行预充电操作,A10拉高即是选中所有BANK

2.进行预充电操作后需要等待一定的时间,即tRP,在此期间同样需要发送NOP空指令(发送空指令是为了防止对SDRAM进行误操作)

3.等待结束后发送自动刷新指令

4.进行自动刷新操作后需要等待一定的时间,即tRFC,在此期间同样需要发送NOP空指令(发送空指令是为了防止对SDRAM进行误操作)

5.重复进行发送自动刷新指令与等待tRFC

6.tRFC等待时间结束后,SDRAM 自动刷新完成

3、状态机

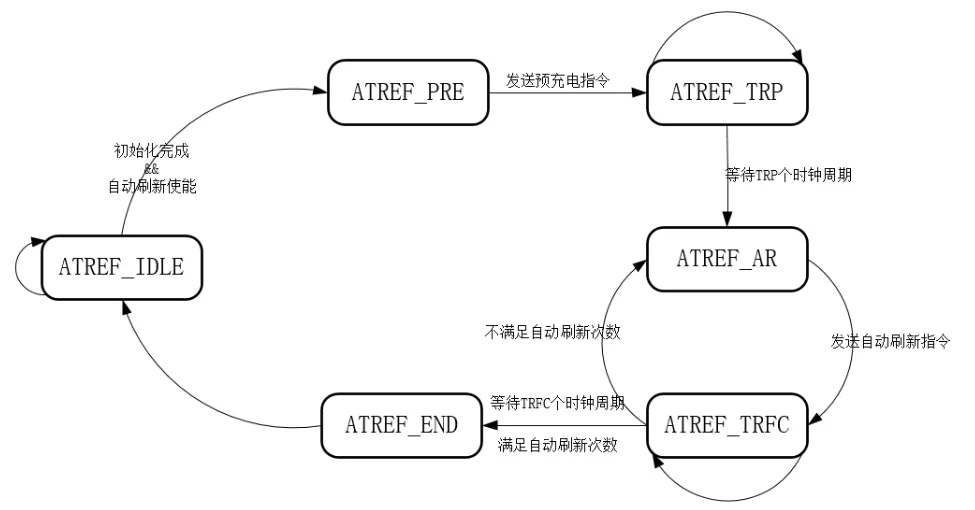

根据自动刷新的时序图,不难绘制出如下状态机:

对各个状态、状态跳转条件、输出进行说明:

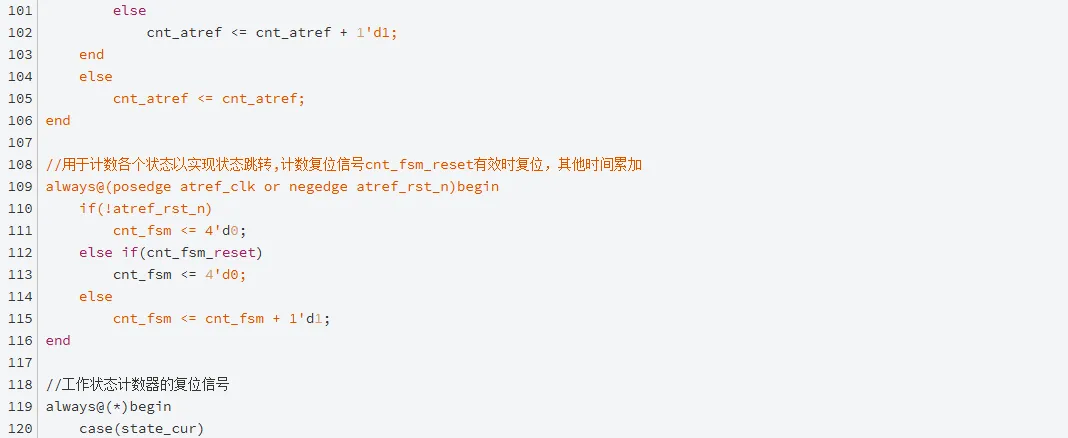

ATREF_IDLE: 初始状态,直到初始化完成后且仲裁模块发送自动刷新使能信号后,跳转至下一状态ATREF_PRE,在此状态发送NOP指令

ATREF_PRE: 发送预充电指令状态、只维持一个时钟周期、下个时钟就跳转到状态ATREF_TRP,在此状态发送预充电指令

ATREF_TRP: 预充电指令等待状态、在此状态等待时间满足TRP后就跳转到下一个状态ATREF_AR,在此状态发送NOP指令

ATREF_AR: 发送自动刷新指令状态、只维持一个时钟周期、下个时钟就跳转到状态ATREF_TRFC,在此状态发送自动刷新指令

ATREF_TRFC: 自动刷新指令等待状态、在此状态等待时间满足TRFC时进行判断,若自动刷新次数满足要求(2次)后就跳转到下一个状态ATREF_END,在此状态发送NOP指令,若不满足自动刷新次数要求就继续进行自动刷新操作,跳转到状态ATREF_AR

ATREF_END: 自动刷新结束状态,完成自动刷新后停留在这个状态一个周期;在此状态发送NOP指令,并发送一个自动刷新完成脉冲信号以通知仲裁模块自动刷新结束

4、接口定义与整体设计

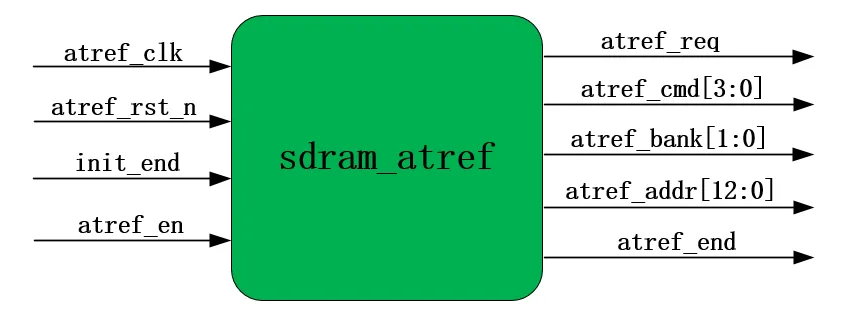

Verilog编写的SDRAM自动刷新模块的整体框图、输入输出信号如下所示:

其中信号描述如下表:

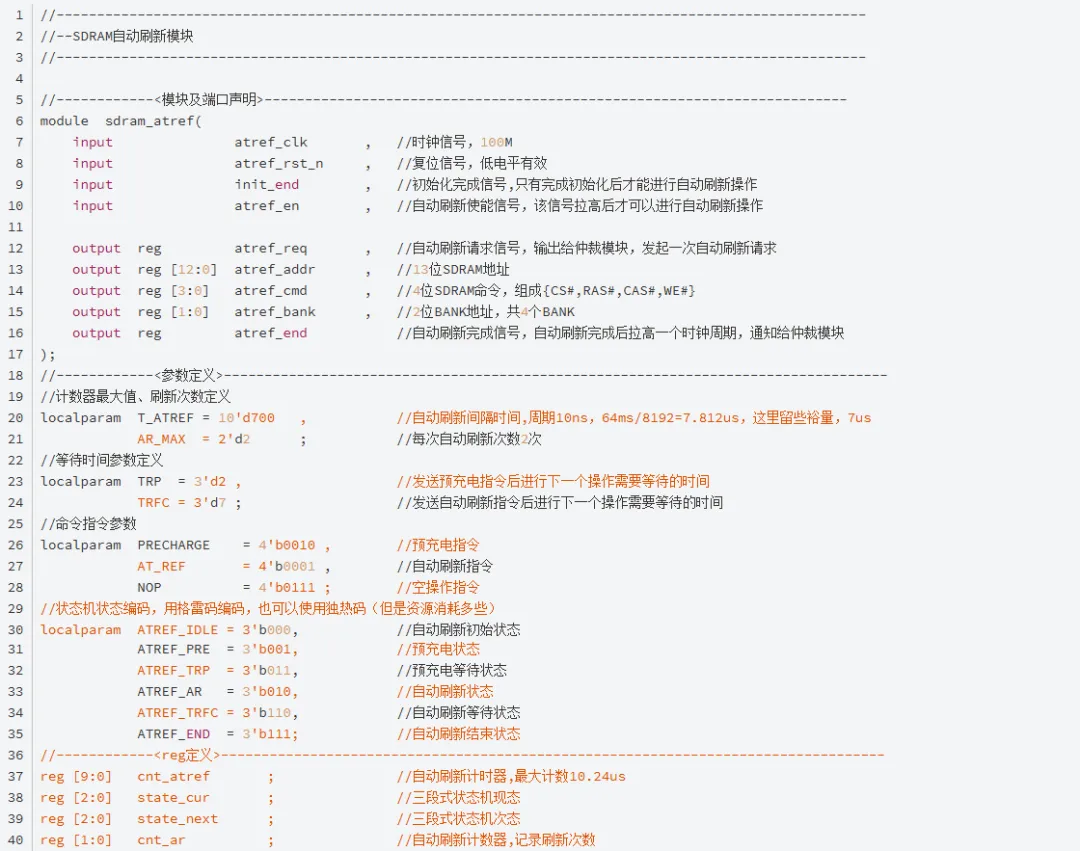

5、Verilog代码

有如下两点需要特别注意:

自动刷新机制:

因为SDRAM的操作有自动刷新、和读、写。在SDRAM进行刷新的时候,肯定是不能进行读或写,同理,进行读写的时候也不能进行自动刷新,为了反正自动刷新与读写冲突、或者读、写冲突,所以或许还需要设计一个仲裁模块。

当自动刷新模块需要进行自动刷新时,需要给仲裁模块发送自动刷新请求,仲裁模块根据当前SDRAM的工作状态进行判断,能否响应这个自动刷新信号;当自动刷新信号可以被响应,仲裁模块发送自动刷新使能给自动刷新模块。自动刷新模块接收到使能信号后开始进行自动刷新操作,刷新完成后发送结束信号给仲裁模块,以便仲裁模块进行下一次的判断。

自动刷新时间:

根据数据手册,可知道MT48LC64M4A2的刷新要求是 64ms完成所有行(8192行)的刷新,换算下来就是7.8125us要完成一次刷新操作。考虑到裕量,这里通过localparam例化的方式将其选定为7us。

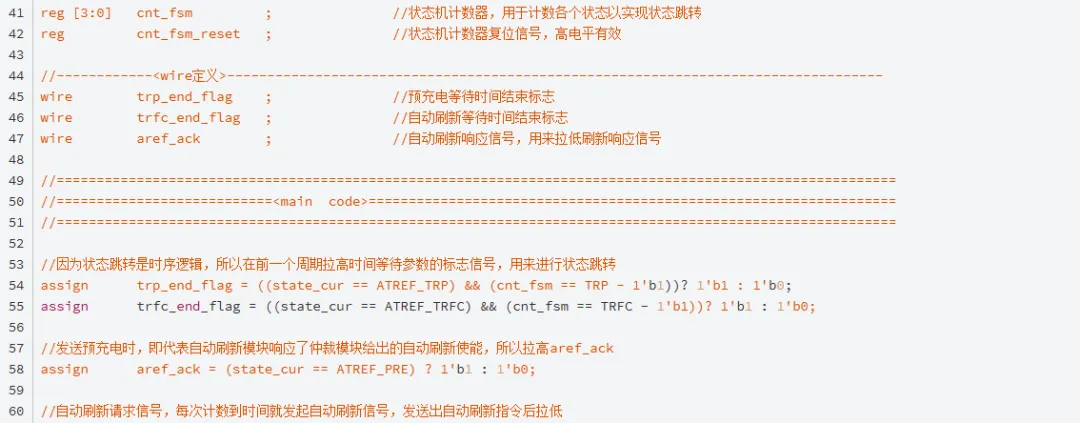

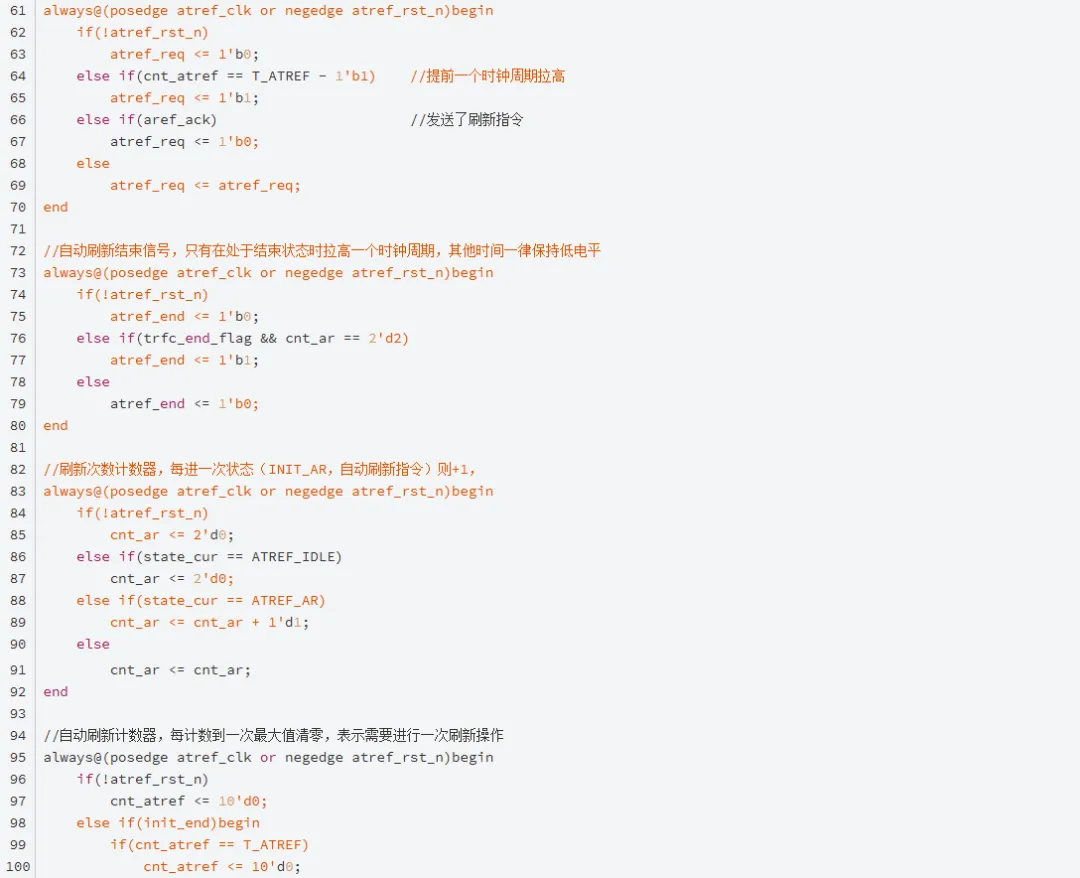

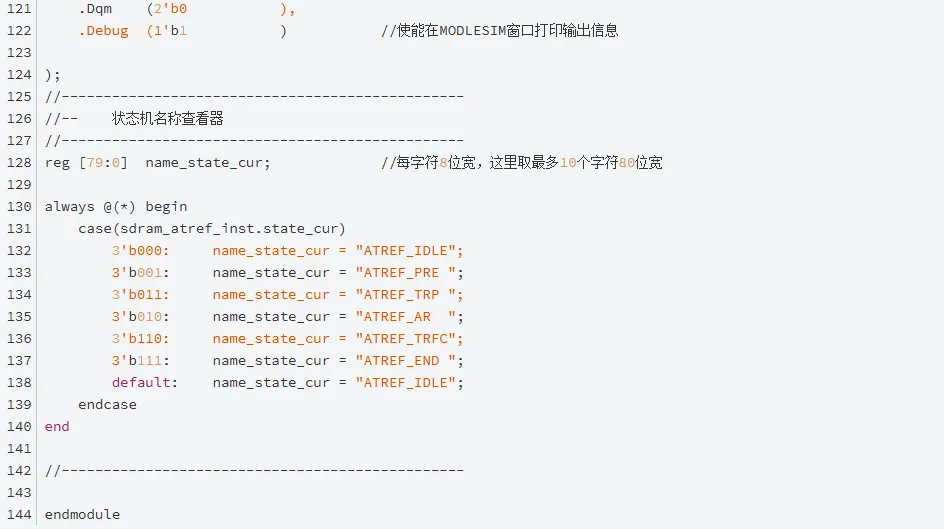

根据上述状态机描述、整体设计不难编写出模块实现的Verilog代码:

代码是用三段式状态机写的,其实用线性序列机也可以,只是三段式的会规范点。

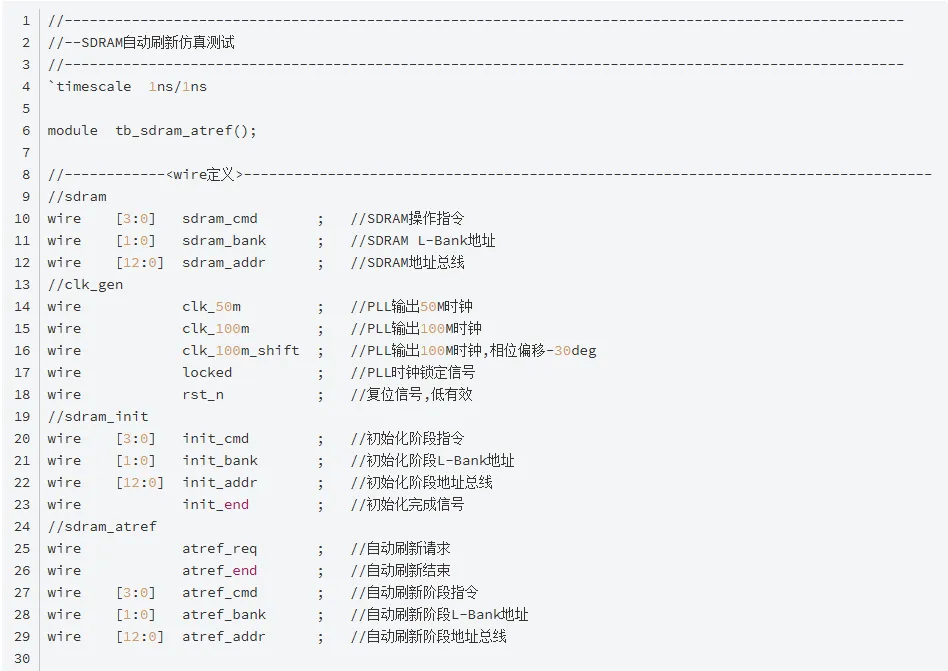

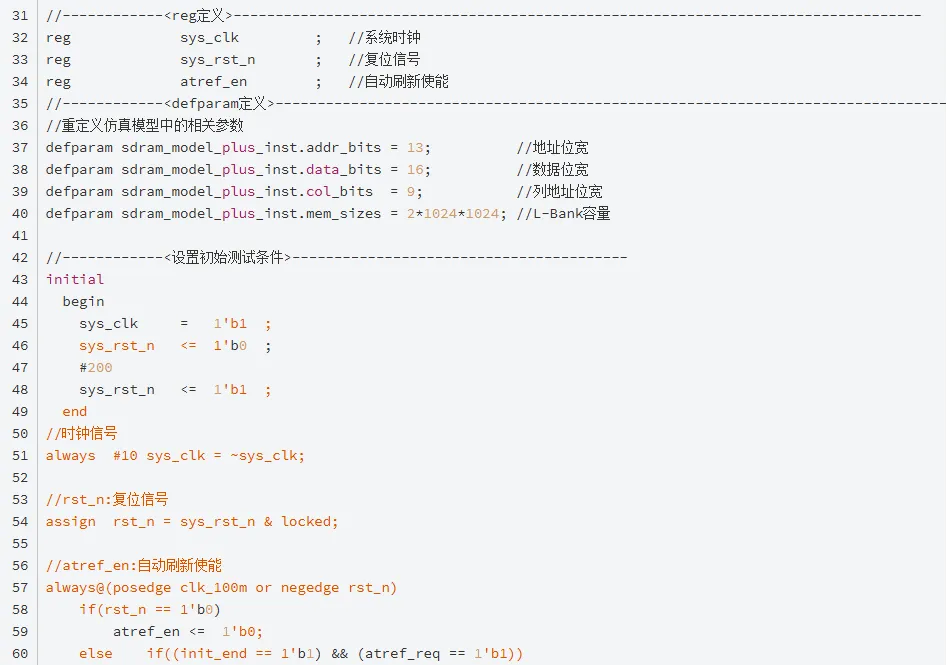

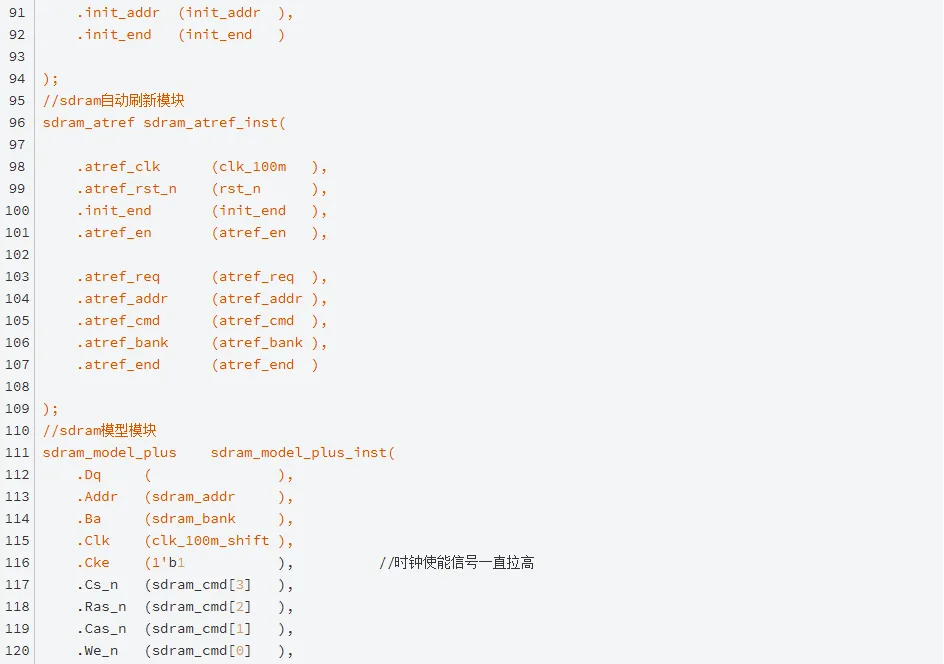

6、Testbench

Testbench除了例化了上面编写的SDRAM初始化模块外,还例化了一个PLL模块,分别输出50M、100M和相位偏移-30°的100M时钟信号(PLL模块就不给出了,都看到SDRAM了,不可能PLL都不会吧?),还有之前设计的SDRAM初始化模块,SDRAM的所有操作都需要在初始化完成后才能进行。

除此之外还例化了一个网上找的SDRAM的仿真模型sdram_model_plus,作者是李晟、陈乃奎、罗瑶。

7、仿真结果

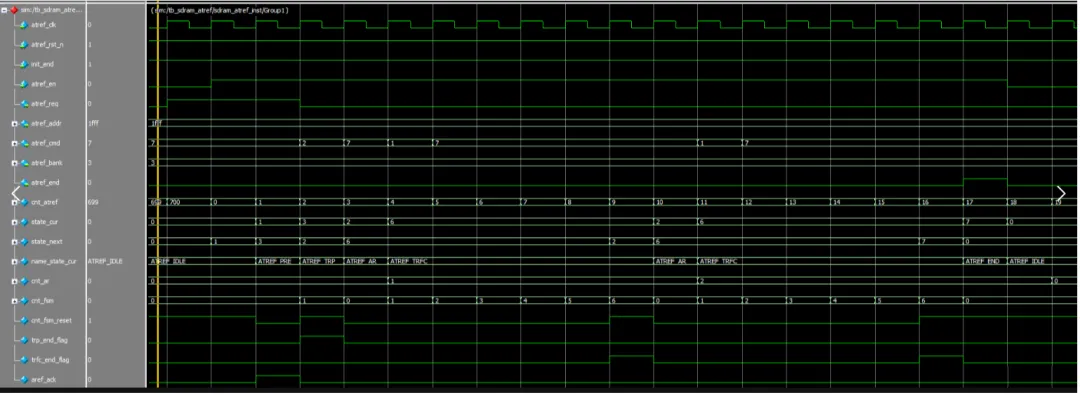

仿真结果截取如下:

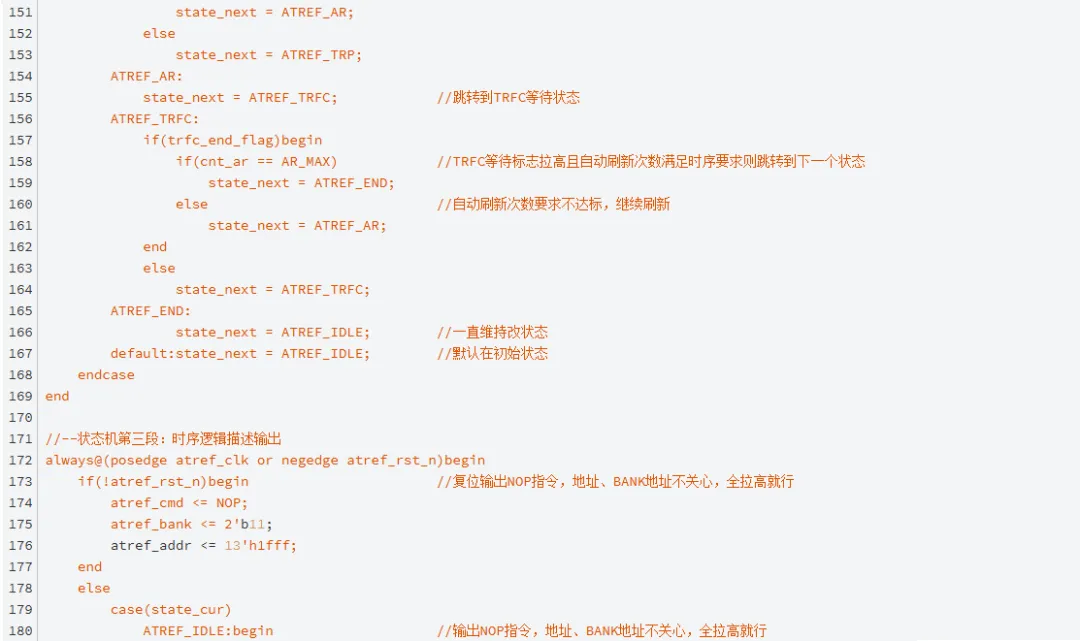

上图:

在计数器cnt_atref计时到700后清零,此时init_end为高电平,所以拉高自动刷新请求

仲裁模块(模拟的)接收到刷新请求后发送刷新使能信号给自动刷新模块

自动刷新模块接收到刷新使能信号后跳转到预充电状态ATREF_PRE

发送预充电指令后,进行等待,满足2个时钟的TRP时序要求后进行第一次自动刷新操作

发送第一次自动刷新操作指令后,进行等待,满足7个时钟的TRFC时序要求后机型第二次自动刷新操作

等待到满足7个时钟的TRFC时序要求后跳转到状态ATREF_END

在状态ATREF_END拉高atref_end一个周期,通知给仲裁模块自动刷新操作完成

因为输出是用的时序逻辑,所以输出会落后条件一个时钟周期

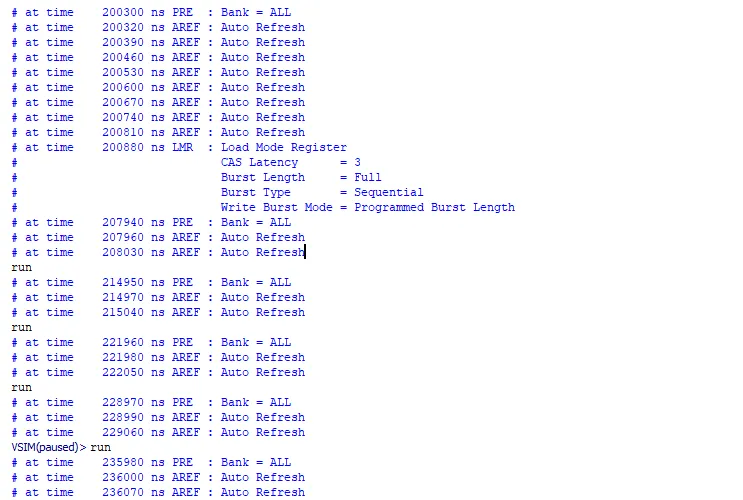

modlesim命令窗口打印的信息如下:

可以看到:

在第一次初始化完成后约7us后进行了第一次自动刷新操作;

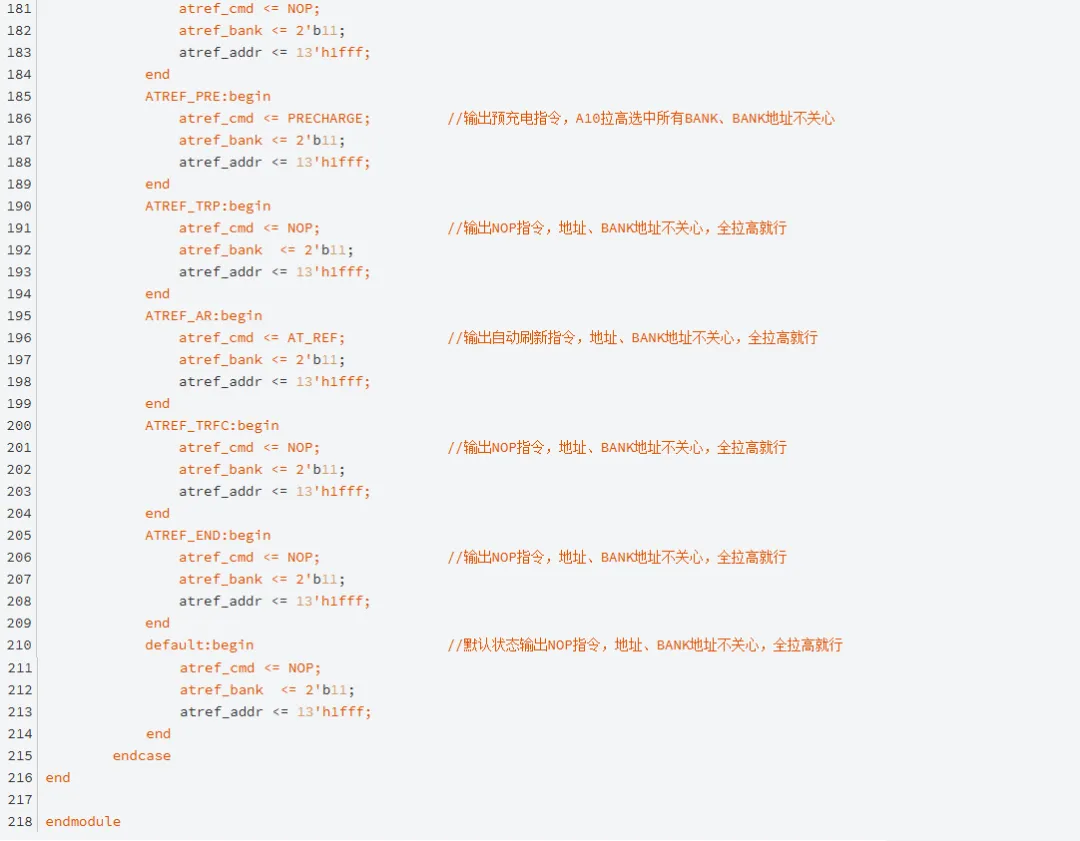

后续的几次自动刷新操作间隔为7us 。