作者:数字站

概述

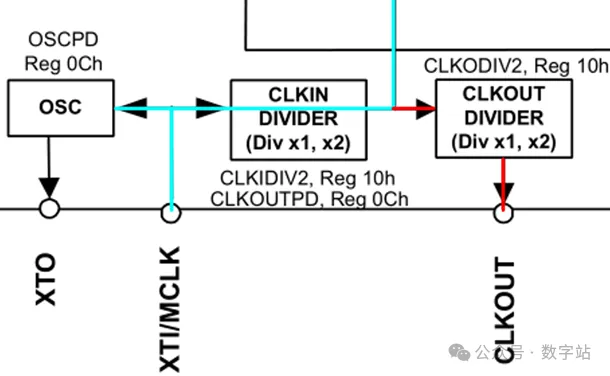

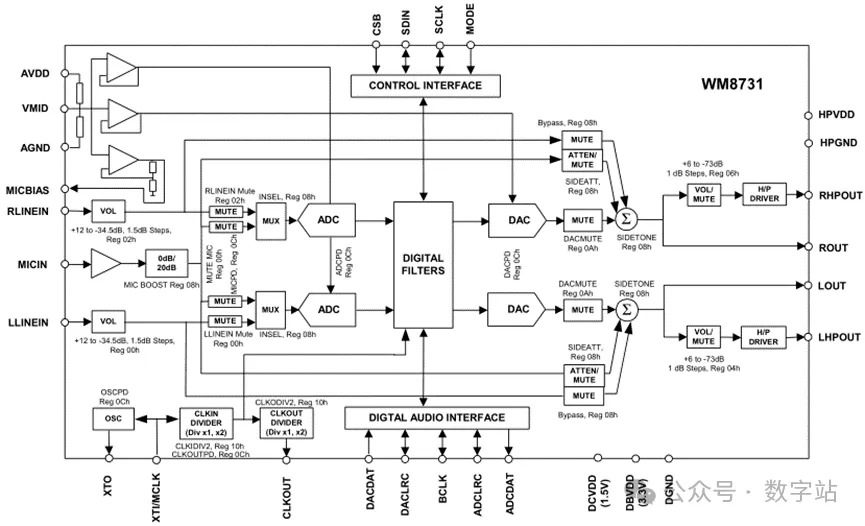

WM8731是集成耳机驱动器的低功耗立体声编解码器,有2路24位的ADC及DAC,支持16~32位的数字音频输入字长和8kHz~96kHz的采样速率,芯片结构框图如下所示。

上半部分包含四个配置寄存器相关的信号,下边中间包含5个I2S协议传输数据的信号,下边左侧是外部主时钟输入端口,左侧包含两路音频输入信号,右侧包含左右两声道的音频输出信号。

图1 芯片结构框图

该芯片有两路音频输入,一路音频输出,其中MICN是麦克风输入,信号进入芯片沿天蓝色信号经过可编程放大器(放大0~20db)后接入两路ADC输入,如果启用侧音模式,则不会进入ADC,而是经过紫色走线直接传输到输出管脚的位置,实现音频信号的环回。

MICN输入时,两个ADC采集的数据是相同的。如果音频从RLINEN/LLINEN输入,则两个ADC采集传输左右双声道的不同数据,在环回模式下同样会绕过ADC,直接叠加在DAC输出上。

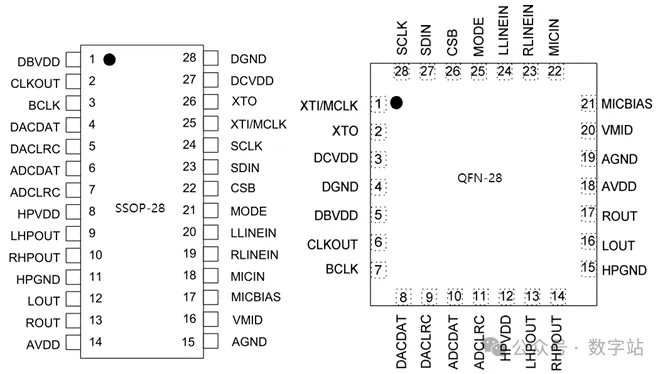

该芯片包含SSOP-28和QFN-28两种封装形式,如下所示。

图2 芯片封装

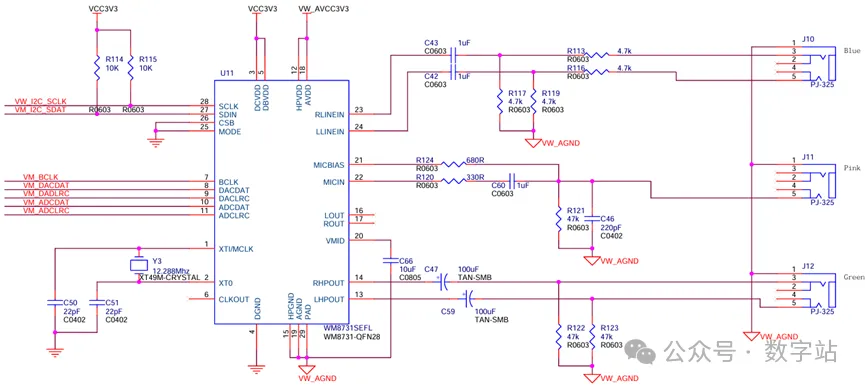

该芯片对应模块的原理图如下所示,右侧是两路音频输入(使用时只能选择其中一路)和一路音频输出,左侧是配置内部寄存器端口信号、I2S接口部分和时钟输入部分。

图3 模块原理图

对应的模块如下图所示,其中蓝色是RLINEN/LLINEN音频输入座子,粉红色是麦克风音频输入座子,青色是音频输出座子。

图4 WM8371模块

该芯片只有11个9位寄存器。后续会讲解每个寄存器的使用,及对应的电路设计,从而分析出原理图的设计思路和后续配置寄存器参数的参考规则。

详解寄存器

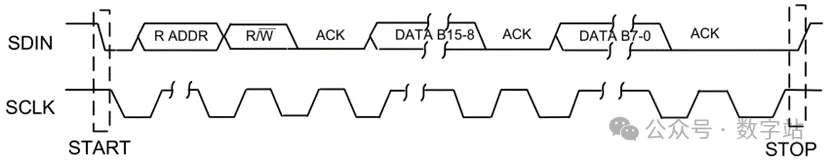

首先需要了解如何配置内部寄存器,WM8371提供了两种总线配置方式,MODE管脚为低电平时,选用I2C总线配置内部寄存器,对应时序如下所示。

图5 I2C时序

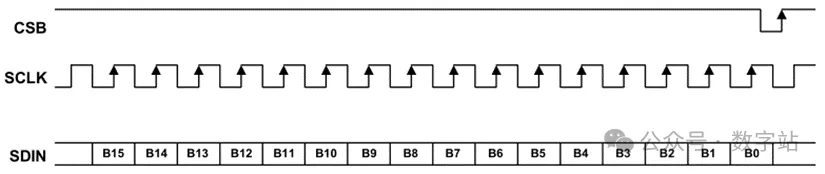

当MODE为高电平时,选用三线模式配置内部寄存器,WM8371在SCLK上升沿采集SDIN的数据,在CSB上升沿锁存16位数据,高7位数据为寄存器地址,低9位是写入寄存器的数据。

图6 三线模式时序

由图3原理图知,该模块的MODE接地,因此只能使用I2C时序配置内部寄存器,前文详解过I2C时序,本文不再赘述,点击查看。

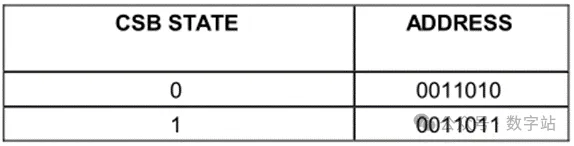

注意在使用I2C时序配置内部寄存器时,CSB作为I2C器件地址的最低位,即同一I2C总线上最多可以挂两个WM8731,通过CSB不同状态进行区分。I2C器件地址如下所示。

图7 I2C器件地址

左右声道线路寄存器(reg0 & reg1)

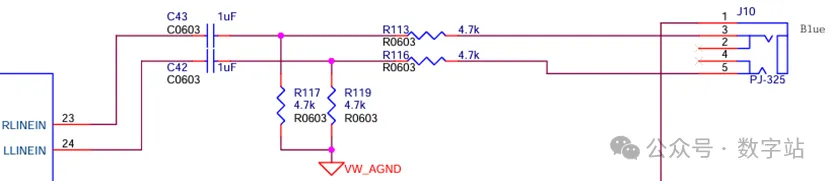

该部分芯片外部电路设计如下图所示,左右两个声道的输入电压经过4.7KΩ分压后输入到管脚中(一般的CD播放器输出电压幅值为2V,而芯片ADC的输入电压范围为1V)。隔直电容C43和C42,与WM8371输入电阻构成一个高通滤波器。

图8 左右声道输入电路

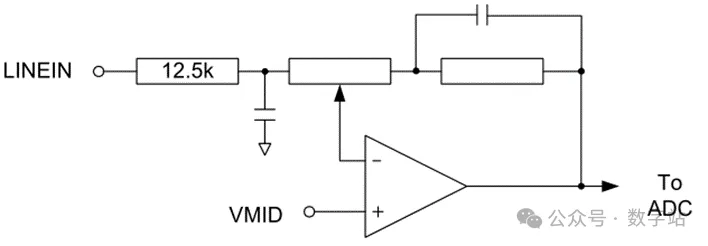

信号进入WM8371后,需要经过下图的放大电路,该电路放大倍数可以通过寄存器在+12dB至–34.5 db范围内以1.5dB步进进行调整。AVDD = 3.3V时,ADC满量程输入为1V,可以通过调整该电路的放大倍数让输入电压在ADC允许的范围内,防止失真。

图9 线路输入原理图

通过设置寄存器0、寄存器1的低5位数据来调整左、右声道电路的放大倍数,默认值为5’b10111,不放大。5’b11111表示将输入信号放大12db后接入ADC,5’b00000表示将输入信号衰减34.5db后接入ADC,如下图所示。

第7位LINMUTE用于控制是否将左、右声道的两路输入信号接入ADC,注意此处设置为0只能限制左右声道输入不能进入ADC,但依旧能够在回环模式下叠加到DAC的输出线路上。

图10 左右声道输入路径寄存器设置

两个声道可以单独设置为放大倍数。如果两个通道使用相同参数,则可以将第8位拉高,之后配置其中一个通道后,另一个通道也会使用相同参数,减少寄存器配置的次数。

耳机放大器(reg2 & reg3)

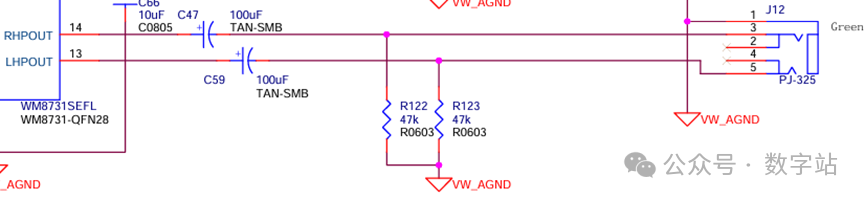

耳机的输出电路如下图所示,隔直电容C47、C59将RHPOUT、LHPOUT的直流与耳机隔离。下拉电阻R122、R123让C47、C59放电,防止耳机连接处的电压上升到可能损坏耳机的水平。

图11 耳机输出电路

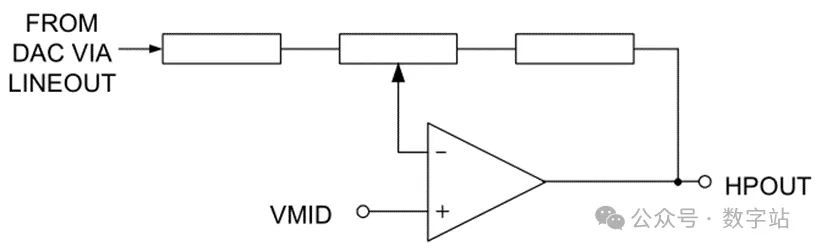

DAC输出信号经过下图的放大电路后到达HPOUT端口,可以通过内部寄存器调整左、右两声道DAC输出放大器的放大倍数,进而调整两个耳机的音量。

图12 耳机放大器原理图

对应的寄存器如下所示,低7位数据用于调整左、右两声道输出放大器的放大倍数,调整范围是-73db至+6db,调整步进位1db,默认0db(不放大)。

图13 左右声道输出路径寄存器设置

左、右声道还可以启用各自的过零检测器,通过第7位配置。两个声道可以独立不同配置参数,也可以通过启用第8位使两个通道使用同一套参数,减少寄存器配置次数。在使用使,这两个寄存器可以保持默认值。

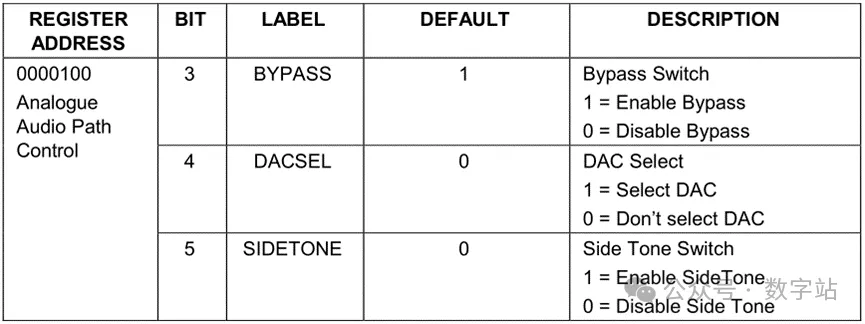

模拟音频路径控制(reg4)

麦克风音频输入的电路图如下所示,R121和R124构成偏置网络的一部分,只有需要偏置电压的驻极体话筒才需要连接到MICBIAS的R124。R121应始终存在,防止麦克风输入充电到高电压损坏连接的麦克风。C46与麦克风的源阻抗和MICIN的输入阻抗构成RF滤波器。

图14 麦克风输入电路

MICBIAS输出提供低噪声基准电压,MICBIAS生成电路如下图所示,由于MICBIAS的最大电流能力为3mA,外部偏执电阻R124和R121的阻值不能太小。

图15 麦克风偏置示意图

麦克风信号进入WM8371后,需要经过下图所示电路才能进入ADC,同样可以调整放大倍数(音量)。下图包含两个反相运算放大器电路,第一级放大电路的增益为G1 = 50KΩ / (R120 + 10kΩ)。由于图14中R120为330Ω,则第一级放大电路的放大倍数约等于5倍。

图16 麦克风输入原理图

通过调整R120的阻值来调整第一级放大电路增益,调整范围-6db至14db。第二级可以配置为0db或者20db增益,因此可以满足–6dB至34dB范围内输入信号的所有增益。

寄存器4的第0位用于设置麦克风输入的第二级启用或禁用20db增益,第1位用于控制是否将麦克风管脚的输入信号接入ADC。

图17 麦克风输入软件控制

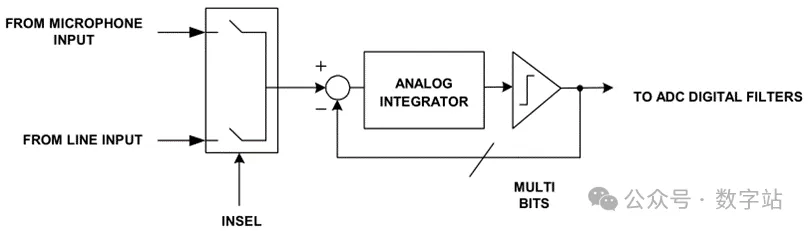

WM8371内部的ADC的原理图如下所示,输入可以来自麦克风音频输入管脚,也可以来自左、右两声道音频线路输入管脚,通过寄存器4的第2位进行配置。

图18 ADC原理图

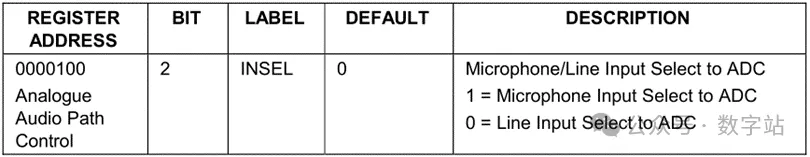

如下图所示,寄存器4的第2位配置为高电平时,选择麦克风音频输入接入ADC,否则选择左、右声道的音频输入接入到ADC。

图片图19 ADC软件控制

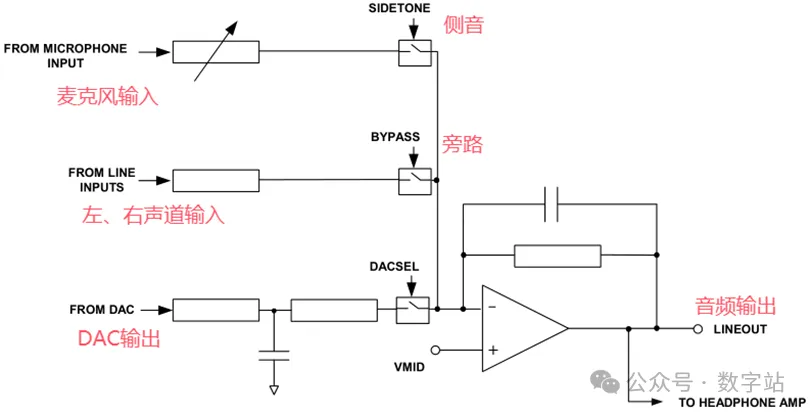

该寄存器还用于设置麦克风音频输入和左右声道输入回环及DAC输出使能,如下图所示。注意这三路输出是叠加的,因此在选用其中一路时,另外两路应该关闭,不然可能会出现噪声。

图20 音频输出原理图

第3位配置为高电平时,左、右两声道的音频输入绕过ADC,直接输出到上图中输出放大器的输入端。

第4位使能DAC输出信号,用户在使用I2S输出音频信号时,一定要将该位设置为高电平,否则DAC输出信号与音频输出管脚是断开的。

图21 输出软件控制

第5位为高电平时,麦克风音频输入绕过ADC,直接叠加到输出放大器的输入端。麦克风输入在侧音模式下可以通过该寄存器的第6位和第7位设置路径的衰减倍数。

图22 侧音模式衰减

该寄存器主要用于控制麦克风输入电路的第二级放大倍数,ADC输入信号的选择,两路输入信号绕过ADC、DAC直接回环到音频输出的相关设置,相对比较重要。

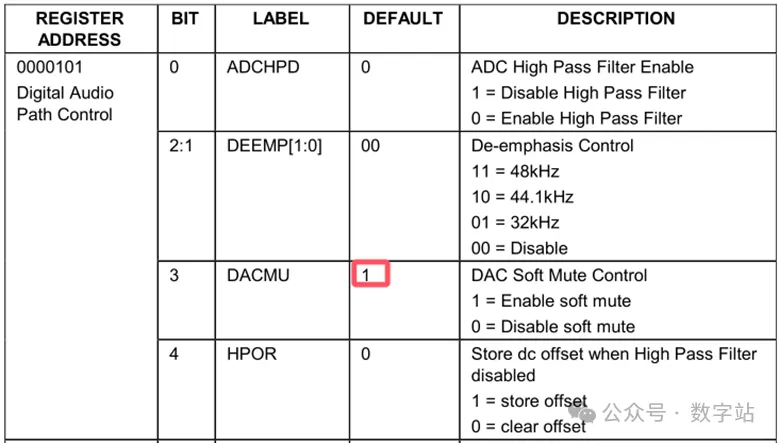

数字音频路径控制(reg5)

该寄存器主要用于设置24位ADC/DAC的输入/输出参数,ADC的输入有一个可选的高通滤波器,通过设置第0位启用,DAC的输出加重,这些保持默认即可,一般不会使用。

图23 ADC及DAC控制寄存器

重点关注上图中第3位,默认为高电平,将DAC输出静音,在使用DAC输出音频时,一定要将该位置为低电平,否则无法听到DAC输出的音频。

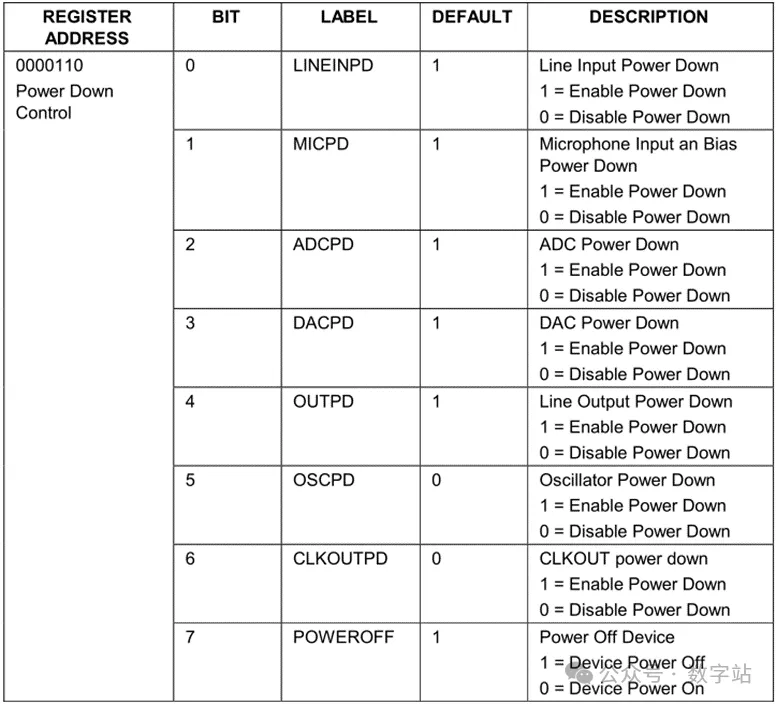

省电模式(reg6)

这里有大坑,wm8371默认将两路音频输入、ADC、DAC、音频输出部分的供电全部断开,如下图所示。所以上电后一定要配置该寄存器,否则可能无法使用大部分功能。

图24 省电模式寄存器

数字音频接口格式(reg7)

该寄存器主要功能是配置I2S接口协议的格式,如下图所示。低2位数据用于配置I2S协议的四种模式,前文已经详解过I2S协议的时序,本文不再赘述,点击查看。

第2位和第3位用于配置音频输入数据的长度,默认为ADC/DAC的数据位宽24位。注意ADC/DAC的数据位宽始终位24位,当IWL[1:0]设置为16位时,ADC的24位输出截取高16位传输给I2S接口,然后发送给主控芯片。当IWL[1:0]设置为32位时,在ADC的24位数据低位拼接8位0后传输给I2S接口,然后发送给主控芯片。I2S在右对齐模式下,不能使用32位数据。

图25 数字音频接口格式寄存器

第4位用于设置DAC左右声道数据的传输,I2S不再DSP模式下时,如果该位为高电平,则DACDAT在DACLRC高电平时传输右声道数据,在DACLRC低电平时传输左声道数据。

第6位用于设置I2S工作模式,主从模式都比较好用。

其余数据位的作用不是很清楚,默认设置即可,低4位和低6位需要重点关注。

数字音频接口格式(reg8)

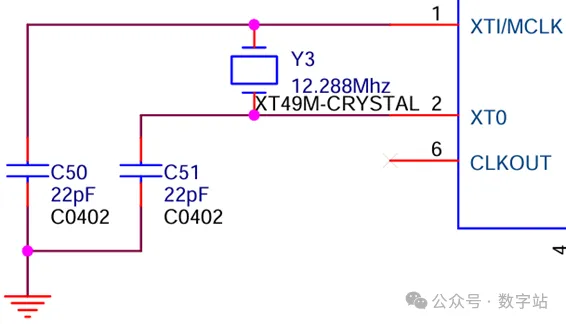

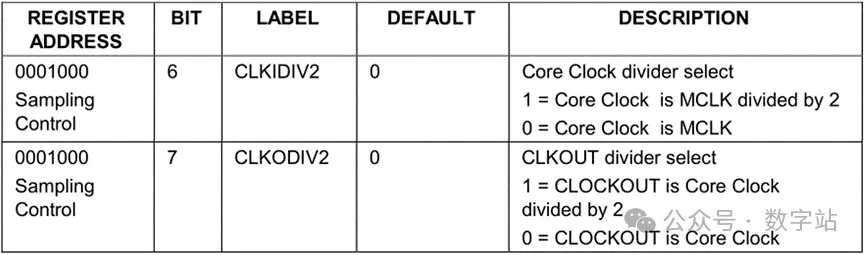

该寄存器用于设置ADC/DAC采样率及系统时钟信号,先将系统时钟相关内容。

对应的电路如下所示,外部输入12.288MHz时钟信号进入XTI/MCLK管脚,CLKOUT悬空。

图26 时钟电路

如下图所示,时钟进入WM8371芯片的MCLK管脚后,先经过一个可编程分频模块,然后进入内核,如下图蓝色走线。还可以通过红色走线,在经过一个分频器后输出到CLKOUT管脚,图26中CLKOUT管脚悬空,则该时钟输出并没有使用。

图27 时钟信号流向

两个分频器对应的寄存器设置如下所示。

图28 分频器参数设置

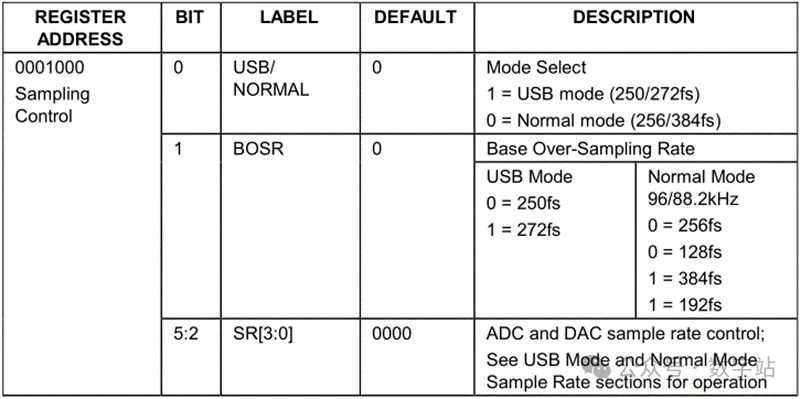

该寄存器其余位用于设置芯片的工作模式以及ADC/DAC采样率,如下图所示。最低位为1时WM8371工作在USB模式(这里的USB与实际的USB并没有什么关系,USB模式下MCLK必须是12MHz,因为USB的时钟也是12MHz,因此叫USB模式)。为0时工作在正常模式下,一般使用正常模式。

图29 采样率控制

第1位到第5位共同设置ADC/DAC的采样率,虽然ADC/DAC采样率可调,但其实只能根据MCLK的频率选择其中几种,并不能实现任意采样率。

图26中MCLK输入频率为12.288MHz,如下图所示框中所示,如果BOSR为0,SR为4’b0111,则ADC/DAC采样率均为96KHz。

图30 正常模式下采样率设置

由上图知,当MCLK为12.288MHz时,能够设置的ADC/DAC采样率为8KHz、32KHz、48KHz、96KHz,并不能设置成其余采样率,默认使用48KHz采样率。

下图是USB模式下采样率的设置,外部晶振输入时钟只能是12MHz,因此该模块是无法使用该模式的。

图31 USB模式下采样率设置

数字音频接口格式(reg8)

为防止数字音频接口出现任何通信问题,音频接口被禁用(100kΩ下拉三态),寄存器配置结束后向该寄存器写入高电平。

图32 激活DSP和数字音频接口

复位寄存器(reg15)

WM8731/L包含一个上电复位电路,可将器件的内部状态复位到已知状态。

使用软件复位时,在三线模式下,复位在CSB的上升沿有效,在SCLK的下一个上升沿释放。在双线模式下,复位在ACK信号期间有效(约1个SCLK周期)。

图33 复位的软件控制

总结

上述十一个寄存器的配置讲解完毕,需要重点关注省电模式寄存器,音频输入和DAC输出的静音设置,I2S协议的模式和格式设置,采样率的设置,对应框图如下所示。

图34 芯片内部框图

环回模式需要可用于调试模块输入、输出的硬件电路是否正常,也是比较重要的,但要注意各个输入绕过ADC后,是叠加到DAC输出上的,因此需要注意其他路的输出。

本文转载自:数字站微信公众号