作者: 熊猫君Hello Panda,来源:ZYNQ分享客

HyperRAM其实熊猫君很久以前在用了,几年前也分享了一篇实现HyperRAM控制器的博文(博文《Lattice CrossLinkNx LIFCL-40应用连载7-使用HyperRAM存储器》。近期在后台收到好几位朋友咨询一些关于HyperRAM的问题,熊猫君在这里简单的做一个总结。

一、什么是HyperRAM,有什么特点?

(1)技术本质:HyperRAM实际上是一个结合体,它的存储单元是PSRAM(伪静态RAM:它的存储器阵列内部结构类似于 DRAM,但在外部却像SRAM一样运作),接口是HyperBUS,一结合就是HyperRAM。

(2)从哪里来:HyperRAM技术是Cypress(现在被英飞凌收购)在2014发明的,从2015年起开始量产,随后华邦、ISSI等厂商开始跟进推出各自产品。也存在和SPI Flash封装在一起的MCP器件,目前已经发展到16bit位宽的HyperRAM3.0版本。

(3)技术特色:关键技术优势有两个:a)低功耗,静态功耗普遍低于50mW,全速访问功耗也不高;b)HyperBus接口少,比如一个16bit的HyperRAM3.0器件最多只需要21个IO。因此在要求IO占用少,容量和带宽要求适中,有严格功耗限制的场合特别适用。

二、应用场景

结合其技术特色可知,它主要用于低功耗长待机且缓存容量要求较大的场合:

(1)物联网:AIoT领域,特别是需要做触发式音视频和高精度ADC数据样本采集的场合,运营商提供的数据带宽往往无法瞬时上传采集到的数据,低功耗SoC(MCU)内部缓存又不够用时,常常会搭载一颗HyperRAM。

(2)可穿戴设备:特别是健康检测(体征检测)类的应用。

(3)工业设备:很对工业控制和自动化设备里面用到,还有就是热敏感的设备,如红外热成像,国内的一些红外热成像组件和探测器厂商常常会把HyperRAM和低功耗FPGA封装或组合在一起形成低功耗的SoC机芯产品以降低功耗,减少热串扰且提升性能(NETD)。

三、技术方案

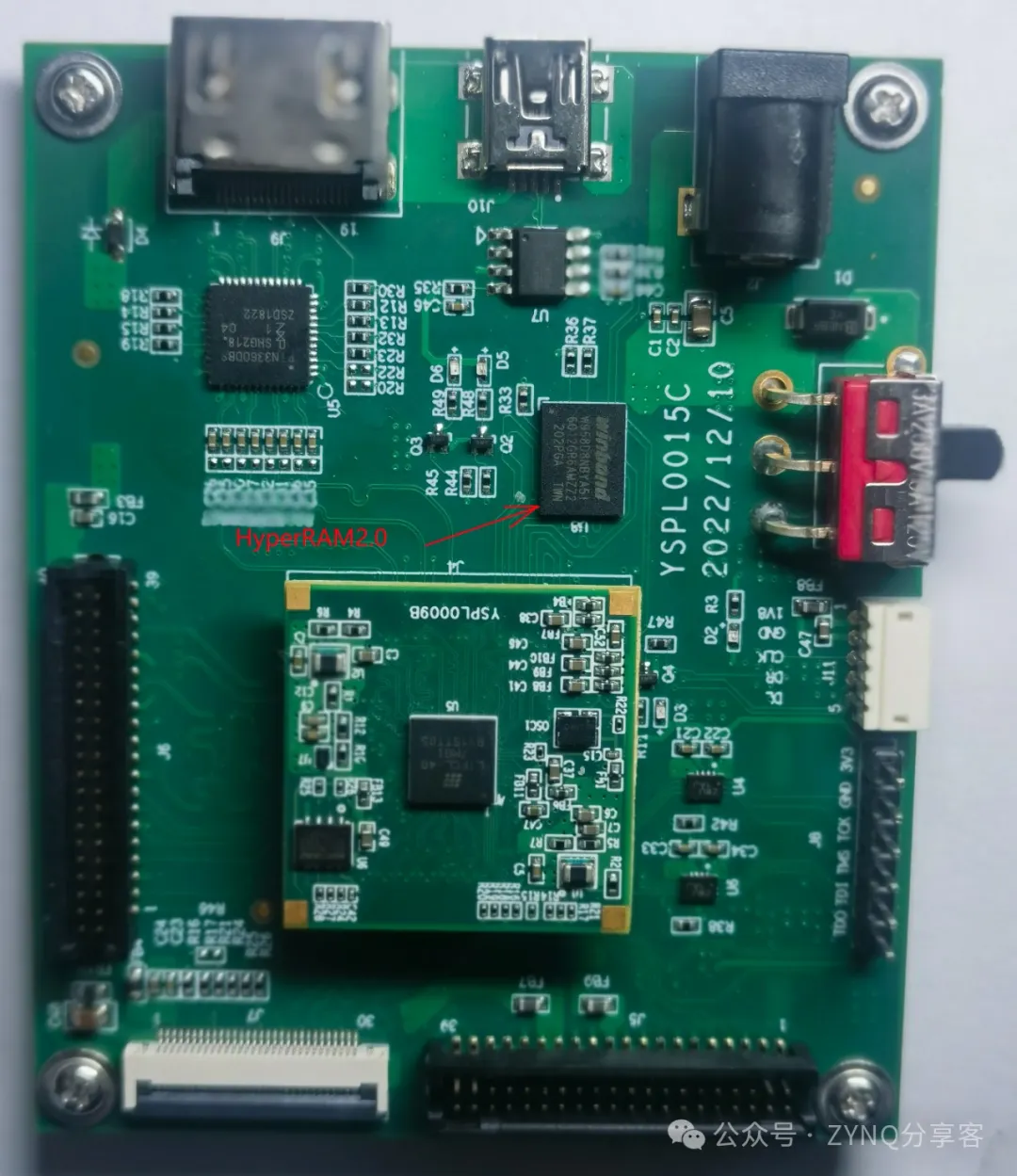

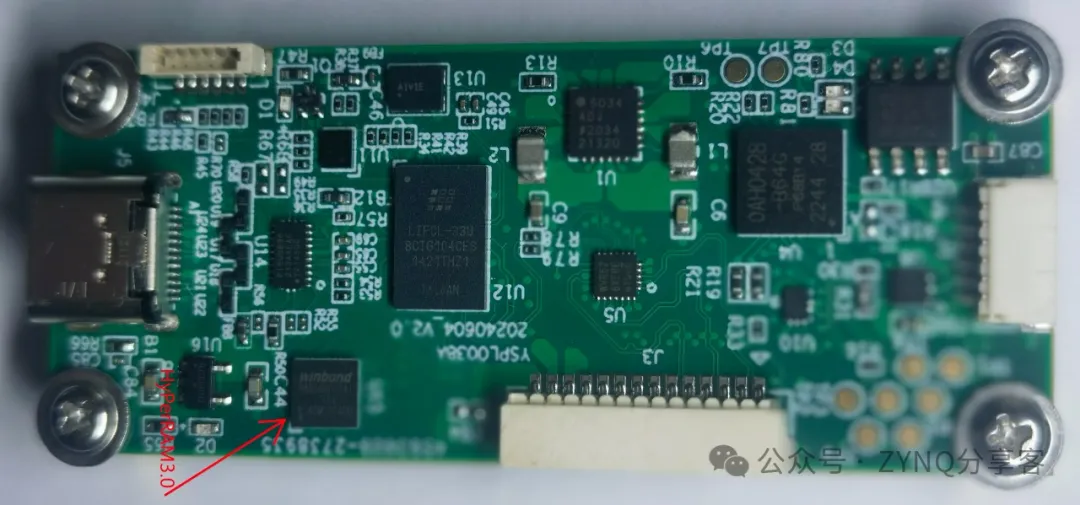

技术方案其实就是低功耗的MCU(SoC)或低功耗的FPGA搭配。熊猫君有几块板子就采用了Lattice低功耗FPGA搭配HyperRAM的做法。如下图(1)HyperRAM2.0 8bit位宽的器件,型号是华邦的W958D8NBYA5I,低功耗FPGA是Lattice CrosslinkNX

LIFCL-40-7MG121I。图(2)HyperRAM3.0 16bit位宽的器件,型号是华邦的W959D6NFKX[512Mb,16bit,250MHz运行频率],低功耗FPGA是Lattice自带USB3.2 Gen1 PHY的LIFCL-33U-8CTG104C。

图(1) HyperRAM2.0器件

图(2)HyperRAM3.0器件

以上开发套件和W959D6NFKX熊猫君均有一些存货,有需要可以联系获取。后台私信留言留邮箱可从熊猫君处获取HyperRAM控制器Verilog源代码。

至于和低功耗MCU(SoC)的搭配方式,自不用多说,这些MCU(SoC)都自带HyperRAM控制器。配置参数使用即可。