文章来源:傅里叶的猫

这是在知乎上看到的一个问题,底下的回复中,有个答案提到了这篇论文:

在FPGA的群里,经常会有人讨论以后Verilog会如何发展?HLS和DLS谁会胜出?用Python来写更快还是现在用的相对多一些的Chisel和SpinalHDL?

自从ChatGPT横空出世,笔者就一直有个观点,随着AI的发展,未来肯定是prompt来直接生成Verilog,而不是用其他高级语言来生成。我们这篇文中要讲的论文,正是如何针对大模型来优化Verilog代码的理解(从代码生成自然语言描述)和生成(从自然语言生成代码)。

在文章最后,我们附上了论文的下载链接。

论文正文

1. 引言

这篇论文提出了一个名为DeepRTL的新型统一表示模型,旨在同时提升Verilog代码的理解和生成能力。研究团队来自香港中文大学和国家EDA技术创新中心,他们指出当前大型语言模型在硬件描述语言任务中存在明显不足,特别是现有方法过于侧重代码生成而忽视代码理解,且自然语言与Verilog代码之间的语义对齐较弱,导致生成的代码质量不佳。

为解决这些问题,研究人员构建了一个高质量的多层次数据集,包含超过6万个开源Verilog模块和200多个专有IP模块。数据集采用创新的标注方法:开源部分利用GPT-4结合思维链技术生成多级描述,经人工验证准确率达90%;专有部分则由专业硬件工程师进行精细标注。这种多层次的标注方式(涵盖行级、块级和模块级)显著提升了数据质量。

在模型设计方面,研究团队基于CodeT5+架构,采用课程学习策略分阶段训练模型,从简单的行级任务逐步过渡到复杂的模块级任务。为准确评估模型性能,他们建立了首个Verilog理解基准,并创新性地引入嵌入相似度和GPT Score等语义评估指标,突破了传统BLEU/ROUGE指标的局限性。

实验结果表明,DeepRTL在Verilog理解任务上显著优于GPT-4等大型模型,即使参数规模较小的220M版本也展现出优异性能。在代码生成任务中,其表现与OpenAI最新的o1-preview模型相当,某些复杂设计案例甚至达到100%的生成成功率。研究还证实,排除过长代码片段和采用课程学习策略对提升模型性能具有关键作用。

这项工作的主要贡献在于:首次实现Verilog理解与生成任务的统一优化,构建高质量多层次数据集,开发更精准的语义评估方法,以及展示出超越现有大型模型的性能。尽管在输入长度和专有数据规模方面仍存在局限,但该研究为硬件设计自动化开辟了新途径。团队已公开相关代码和数据集,为后续研究提供了重要基础。未来工作将探索扩展模型上下文窗口,并尝试将DeepRTL应用于更广泛的EDA任务场景。

2. 目前这方面的研究工作

2.1 EDA中的寄存器传输级(RTL)

RTL是电子设计自动化(EDA)的核心抽象层,用于描述寄存器间的数据流动及逻辑操作,通常通过硬件描述语言(HDL)实现。Verilog作为主流HDL,在本研究中与HDL术语互换使用。传统硬件设计流程依赖人工将自然语言规范转化为HDL代码(Blocklove等,2023),但这一过程易引入错误且效率低下。自动化转换能显著提升设计可靠性,而AI技术的进步(尤其是端到端代码生成能力)为此提供了可能。Verilog的详细说明见附录A。

2.2 LLM在EDA中的革新

大型语言模型(LLM)正重塑硬件设计范式(Chen等,2024)。研究表明,LLM在Verilog代码生成(Thakur等,2023;Liu等,2023b)、RTL设计(Blocklove等,2023)及EDA脚本编写(Wu等,2024)中展现出潜力,可降低专业门槛并加速开发(Fu等,2023)。然而,现有公开数据集存在规模小(如Thakur等(2023)仅200样本)、复杂度不足(Liu等,2023b)或标注质量存疑(Zhang等,2024)等问题,制约了模型性能。

2.3 面向Verilog生成的LLM优化

尽管GPT-4等通用LLM具备代码生成能力(Achiam等,2023),但其硬件设计输出仍不完善(Fu等,2023)。近期研究通过微调开源LLM(如基于AST模板的方法(Chang等,2024b))提升了Verilog生成质量,但现有方法多局限于行级代码或缺乏语义关联。为此,我们构建了首个多层级(行/块/模块)对齐的自然语言-Verilog数据集,结合开源与专有代码,同时覆盖生成与理解任务,为开发统一模型DeepRTL奠定基础。

2.4 课程学习的应用

受人类学习机制启发,课程学习通过渐进式训练提升模型性能(Bengio等,2009),已在NLP(Xu等,2020)和代码生成(Na等,2024)中验证有效性。本研究利用多粒度数据集,采用课程学习策略训练DeepRTL,显著提升了其在复杂Verilog任务中的表现。

3. 数据集与理解基准

在本节中,我们介绍了为增强Verilog理解和生成而设计的数据集,该数据集通过行级、块级和模块级的详细及高层描述,将自然语言与Verilog代码对齐。通过整合开源和专有代码,该数据集提供了涵盖广泛硬件设计复杂性的多样化、高质量集合。我们采用GPT-4结合思维链(CoT)方法进行标注,人工评估显示其准确率约为90%,验证了数据集的高质量和可靠性。此外,我们还首次引入了Verilog理解的基准,为评估LLM在解释Verilog代码方面的能力设立了新标准。

3.1 数据来源

我们的数据集包含开源和专有Verilog代码。开源部分通过GitHub关键词“Verilog”收集.v文件,并将其分割为独立模块(每个模块代表Verilog设计中的一个功能单元)。由于当前LLM的上下文长度有限,这种分割对后续标注和微调的高效性和准确性至关重要。我们使用MinHash和Jaccard相似度指标进行去重,并排除主要由注释组成或缺少完整module和endmodule结构的模块。最终,我们获得了61,755个独特的Verilog模块。专有部分包含一组采购的知识产权(IP),增强了数据集的多样性和功能覆盖。这部分包含213个高质量、符合行业标准的Verilog模块,不仅提供了高级功能,还补充了开源数据中未涵盖的独特设计细节。

3.2 数据集标注

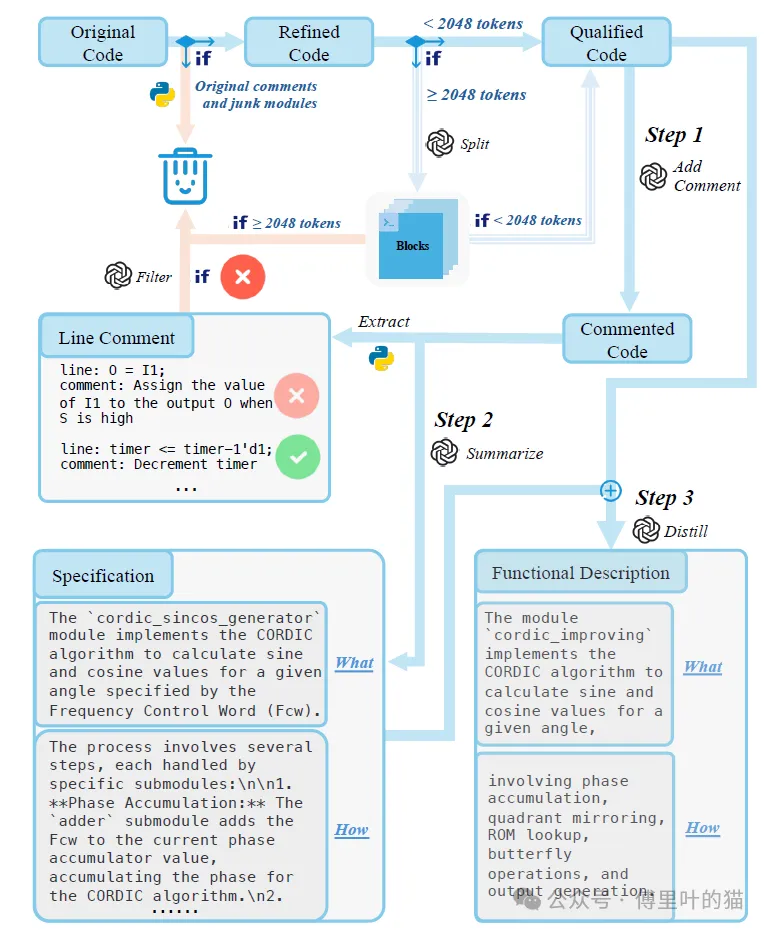

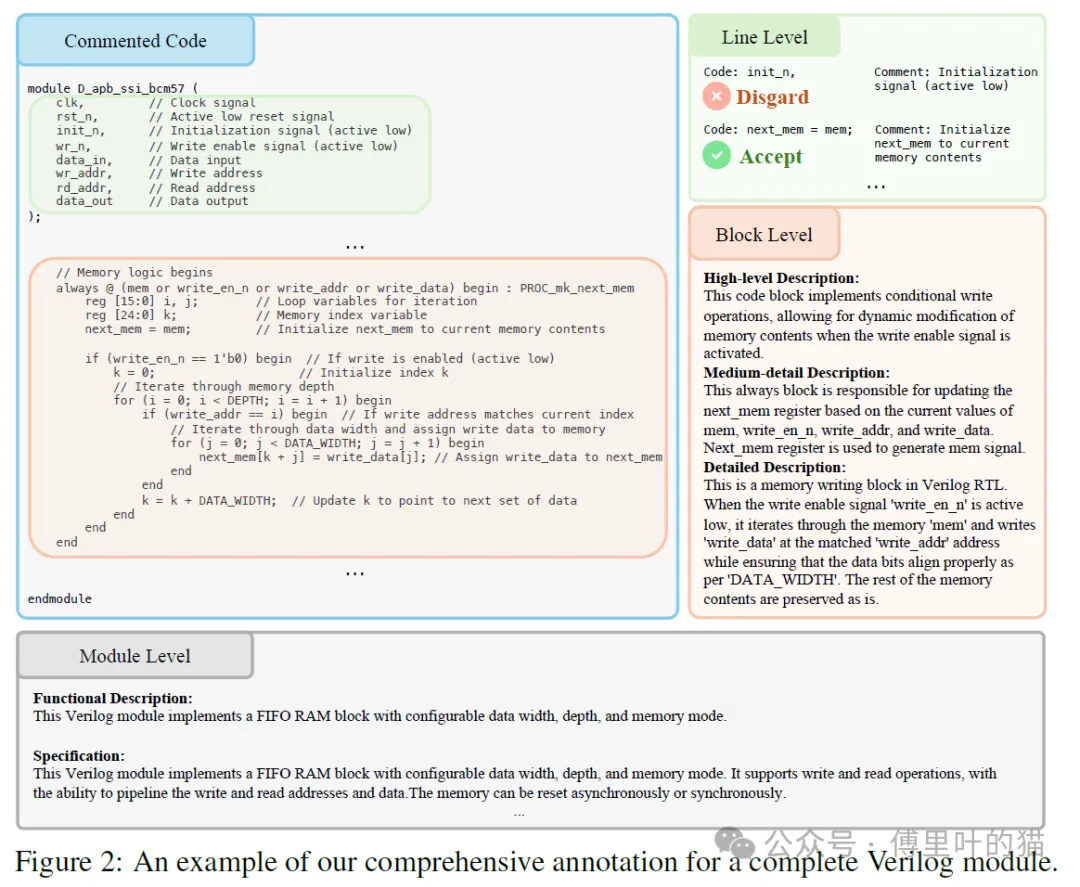

我们对开源和专有代码采用不同的标注策略。对于开源代码,我们使用当前最先进的LLM GPT-4结合CoT方法,提供多级标注。如上图所示,我们首先从原始Verilog代码中移除所有注释(得到精炼代码),以避免错误或误导性注释对训练的干扰。如果完整模块的token数超过CodeT5+的最大上下文长度2048,则使用GPT-4将其分割为更小的可管理块(如always块)。如果分割后的块仍超过2048 token,则将其丢弃。对于token数低于2048的模块和块(合格代码),我们使用GPT-4添加信息性注释,生成带注释的代码(步骤1)。从这些带注释的代码中,我们可以提取行级描述(单行代码与自然语言描述的配对)。为确保行内注释的准确性和相关性,我们使用GPT-4-mini严格检查每条注释,确保其严格限定在对应行的上下文中,不引入无关信息。例如,对于代码行O = I1;,若标注为“当S为高电平时,将I1的值赋给输出O”,由于无法从单行代码推断O是输出或S相关,此类描述将被视为不准确并从数据集中排除,以保证训练效果。

在步骤2中,我们使用GPT-4为步骤1的带注释代码生成详细规范,包括两部分:代码功能的总结(做什么)和实现过程的全面解释(如何实现)。最后,在步骤3中,我们将步骤1的合格代码与步骤2生成的详细规范结合,创建高层功能描述。为确保精确性,我们指导GPT-4专注于合格代码,仅将详细规范作为参考。最终的高层描述简洁总结了代码功能(做什么)并概述实现过程(如何实现)。这一标注阶段最为关键且具有挑战性,因为它要求模型深刻理解Verilog,捕捉代码的高层语义。在当前基准和实际应用中,用户通常向模型提供高层功能描述而非详细实现细节,否则需投入大量精力编写详尽说明,耗时且需要专业知识。

考虑到专有代码的工业级质量,我们聘请专业硬件工程师进行标注,确保符合严格的行业标准。这些专家标注不仅精确,还捕捉了设计细节,显著提升了数据集的价值。与GPT生成的标注不同,人工标注额外包含中等详细程度的块级描述。

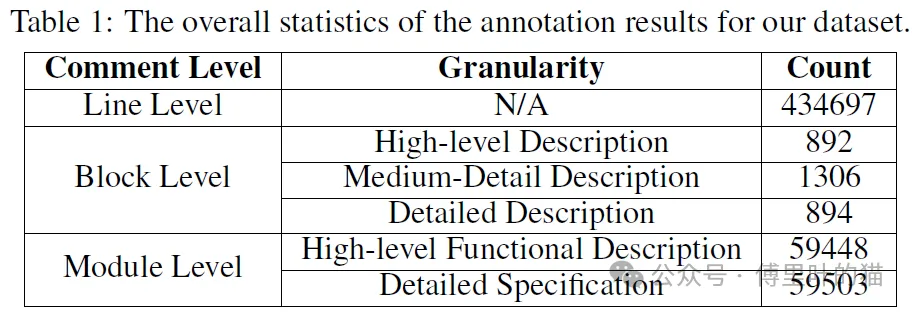

表1展示了标注结果的总体统计。此外,图2展示了一个完整Verilog模块的多级标注示例。值得注意的是,涵盖多级、多粒度描述的数据集将用于训练。类似的工作是Zhang等(2024)提出的MG-Verilog数据集,包含11,000个Verilog代码样本及多级自然语言描述。但其存在以下局限性:

规模较小且缺少专有Verilog代码,降低了多样性和适用性;

采用直接标注而非CoT方法,而我们的实验证明CoT能提升标注准确性(见3.3节);

我们的标注更全面,覆盖行、块、模块级及详细/高层描述,确保自然语言与Verilog代码的强对齐;

MG-Verilog依赖开源LLM LLaMA2-70B-Chat标注,而我们使用最先进的GPT-4。第4.4节将展示LLaMA2-70B-Chat对Verilog的理解较差,导致MG-Verilog标注质量较低。

3.3 数据集评估

为确保数据集质量,我们评估了CoT流程生成的标注。随机抽取200个Verilog模块,由4位专业Verilog设计师评估各级标注的准确性。结果显示:高层功能描述的准确率为91%,详细规范的准确率为88%,行级标注的准确率为98%。此外,我们对比了CoT与直接标注方法(直接从原始代码生成标注),后者准确率仅为67%,凸显了CoT流程的显著优势。

自然语言处理(NLP)领域的最新研究表明,用合成指令数据微调的LLM能更好地理解自然语言指令,并与任务更对齐。需注意的是,我们的工作也使用语言模型生成的数据(包括各级标注)进行微调。尽管并非所有标注都完全准确,但我们实现了约90%的准确率。我们将不准确部分视为数据噪声,微调模型仍能从该数据集中显著受益。

3.4 理解基准

作为首个考虑Verilog理解任务的工作,我们引入了开创性基准,用于评估LLM解释Verilog代码的能力。该基准包含100个高质量Verilog模块,覆盖多样硬件功能,确保对不同类型硬件设计的全面评估。我们聘请4位经验丰富的硬件工程师为每个模块提供精确的功能和实现细节标注,并由另外3位工程师交叉验证,确保准确性,为未来模型评估设立高标准。该基准填补了评估LLM解释Verilog代码能力的空白,后续将公开发布。基准中的详细示例见附录E。

4. 模型与评估

在本节中,我们将介绍DeepRTL,并详细阐述我们的指令微调数据集的构建方式,以及如何采用课程学习策略进行训练。此外,我们还将详细介绍用于评估模型在Verilog理解和生成任务中性能的基准和指标。为了准确评估生成描述在语义上的精确性,我们首次采用嵌入相似度(embedding similarity)和GPT评分(GPT score)进行评估,这两种方法旨在定量衡量模型输出与真实标注之间的语义相似性。

4.1 模型

在本研究中,我们选择对**CodeT5+**进行微调,这是一个基于编码器-解码器架构的代码基础大模型(LLM),适用于广泛的代码理解和生成任务。CodeT5+采用“浅编码器+深解码器”架构,其中编码器和解码器均从预训练检查点初始化,并通过交叉注意力层连接。我们选择CodeT5+进行微调,是因为它已在大量软件代码上进行了广泛的预训练,我们希望通过微调将其学到的知识迁移到硬件代码任务中。此外,该模型的灵活架构允许针对特定下游应用进行定制化训练任务。

CodeT5+采用了一种高效的微调策略,其中深解码器被冻结,仅训练浅编码器和交叉注意力层,从而显著减少可训练参数的数量。具体来说,我们微调了两个版本的CodeT5+:codet5p-220m-bimodal(CodeT5+-220m)和instructcodet5p-16b(CodeT5+-16b),分别得到DeepRTL-220m和DeepRTL-16b。

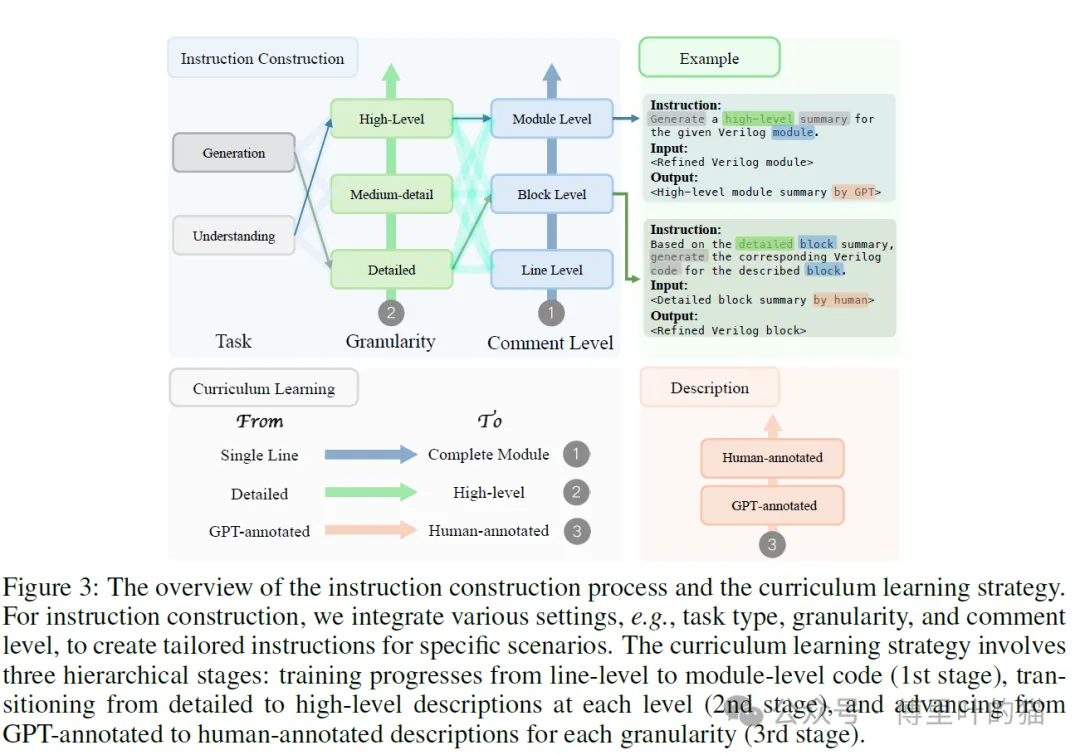

4.2 指令微调数据集

在微调过程中,我们采用指令微调(instruction tuning)策略来增强LLM对不同类型数据和任务的适应性。由于我们的数据集包含多层次的描述,并且模型需要同时支持Verilog理解和生成任务,因此数据和任务的多样性较高。为了适应这种多样性,我们针对每种场景精心设计了特定的指令,以确保模型的输出能够符合预期的指令要求。图3展示了我们如何结合不同的设置(如任务类型、描述粒度和注释级别)来构建针对特定场景的定制化指令,从而优化微调效果。

4.3 基于课程学习的DeepRTL训练

我们采用课程学习(curriculum learning)策略进行微调,充分利用我们结构化数据集中不同层次、不同细节的描述。模型首先在行级和块级数据上进行微调,然后逐步过渡到模块级数据。在每个层级中,我们首先将代码与详细规范对齐,然后再学习高层功能描述。此外,在每个注释粒度上,微调通常从GPT标注的数据开始,然后使用人工标注的数据进行进一步优化。图3展示了这一过程的示意图。

我们采用这种策略,是因为将Verilog模块与其高层功能描述对齐是最具挑战性且最具实际应用价值的任务。这种课程学习策略使模型能够从简单到复杂逐步构建知识。因此,模型在Verilog理解和生成基准测试中均表现出色。需要注意的是,我们排除了基准测试中的案例,确保它们不会出现在训练数据中。

在微调过程中,我们主要遵循CodeT5+的指令微调脚本,但将输入上下文的最大长度扩展至2048个token。我们使用分布式框架DeepSpeed,在配备8块80GB显存的NVIDIA A800 GPU集群上高效微调模型。在推理阶段,我们将温度参数(temperature)调整为0.8(理解任务)和0.5(生成任务),其他超参数保持默认值以确保最佳性能。

4.4 理解任务评估

为了评估LLM在Verilog理解任务中的能力,我们使用第3.4节介绍的基准测试。该评估衡量生成描述与真实摘要之间的相似性。以往的研究通常使用BLEU和ROUGE分数进行评估。BLEU通过计算生成文本中n-gram(即连续的n个词)在参考文本中的出现比例(侧重精确率),而ROUGE则统计参考文本中的n-gram在生成文本中的出现比例(侧重召回率)。然而,这两种指标主要衡量词汇重叠而非语义相似性,可能无法全面反映生成描述的准确性。

为了解决这一局限性,我们首次采用嵌入相似度和GPT评分进行评估。嵌入相似度通过计算生成描述和真实描述的向量表示之间的余弦相似度来衡量语义对齐,其中向量表示由OpenAI的text-embedding-3-large模型生成。GPT评分则利用GPT-4对描述之间的语义一致性进行量化,评分范围为0到1(1表示完全语义对齐)。这些指标通过捕捉描述的语义本质,提供了比传统方法更准确的评估方式。。

4.5 生成任务评估

为了评估LLM在Verilog生成任务中的能力,我们采用Chang等人提出的最新基准测试,该基准基于先前成熟的RTLLM基准进行了扩展。Chang等人的基准测试涵盖了三大类别的广泛复杂度:算术运算、数字电路逻辑和高级硬件设计。与以往研究相比,该基准测试纳入了更多具有挑战性和实用性的Verilog设计,从而更全面地评估模型的代码生成能力。

评估重点关注两个关键方面:语法正确性和功能准确性。我们使用开源模拟器iverilog来评估LLM生成的Verilog代码的语法和功能正确性。在评估指标方面,我们采用广泛使用的Pass@k指标,即如果生成的k个代码样本中有任何一个通过编译或功能测试,则认为问题已解决。在本研究中,我们设置k=1和k=5,更高的Pass@k分数表示模型性能更好。

为了进一步区分模型的能力,我们统计5次生成样本中通过测试的比例,并计算平均成功率。对于语法正确性,该成功率衡量的是成功编译的代码比例;对于功能准确性,则衡量通过单元测试的比例。

5 实验结果

5.1 基线模型

作为基线模型,我们选择了OpenAI的GPT-4-turbo(GPT-4)和GPT-3.5-turbo(GPT-3.5),以及o1-preview模型(OpenAI最新的推理模型,旨在解决包括编程在内的复杂问题)。这些模型是目前最先进的通用大语言模型(LLM),在Verilog生成任务中表现出色。

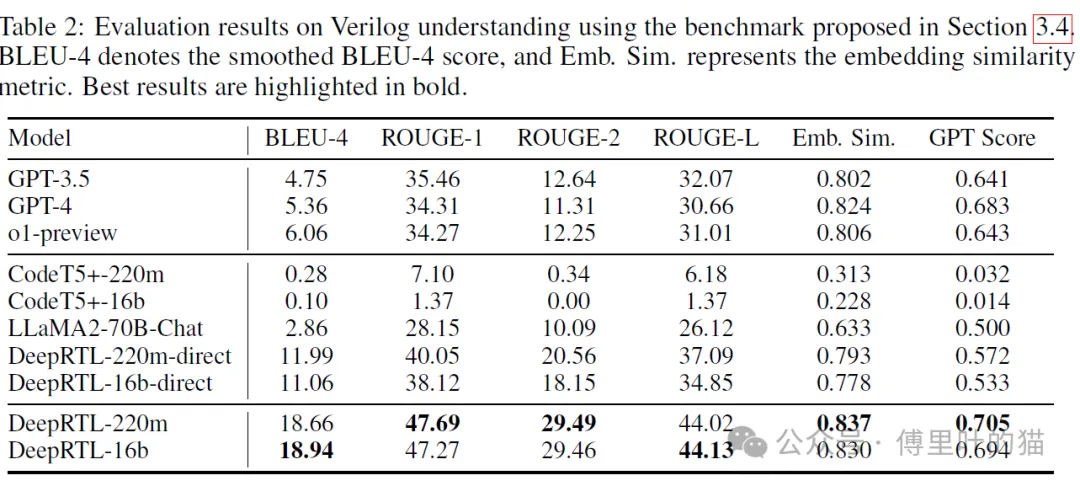

5.2 Verilog理解

如表2所示,DeepRTL在所有评估指标上均显著优于GPT-4。传统的BLEU和ROUGE等指标由于无法准确捕捉语义相似性,评估结果不一致:例如,DeepRTL-16b在BLEU-4和ROUGE-L上表现最佳,而DeepRTL-220m在ROUGE-1和ROUGE-2上领先。相比之下,嵌入相似度(Embedding Similarity)和GPT Score能更准确地评估模型对Verilog代码的理解能力。

与CodeT5+相比,未经课程学习直接训练的DeepRTL-direct(DeepRTL-220m-direct和DeepRTL-16b-direct)的表现凸显了我们数据集的有效性。而采用课程学习策略后,模型性能进一步提升,证明了该方法的优势。此外,LLaMA2-70B-Chat的较差表现也印证了Zhang et al.(2024)的MG-Verilog数据集标注质量不可靠。

为进一步验证模型性能,我们进行了人工评估,结果显示DeepRTL-220m、GPT-4和o1-preview的准确率分别为78%、72%和67%。这些结果与嵌入相似度和GPT Score的评估趋势一致,进一步证明了这些评估方法的有效性。我们发现,DeepRTL-220m优于DeepRTL-16b,这可能是因为CodeT5+-220m在大量成对的软件代码和自然语言数据上进行了预训练,从而实现了更好的代码-语言对齐。相比之下,CodeT5+-16b主要在软件代码数据上预训练,并在合成指令数据上微调,缺乏稳健的代码-语言对齐能力。此外,尽管DeepRTL-220m规模较小,但其性能超越了许多数十亿参数规模的模型,这归功于我们数据集的高质量和课程学习策略的有效性。

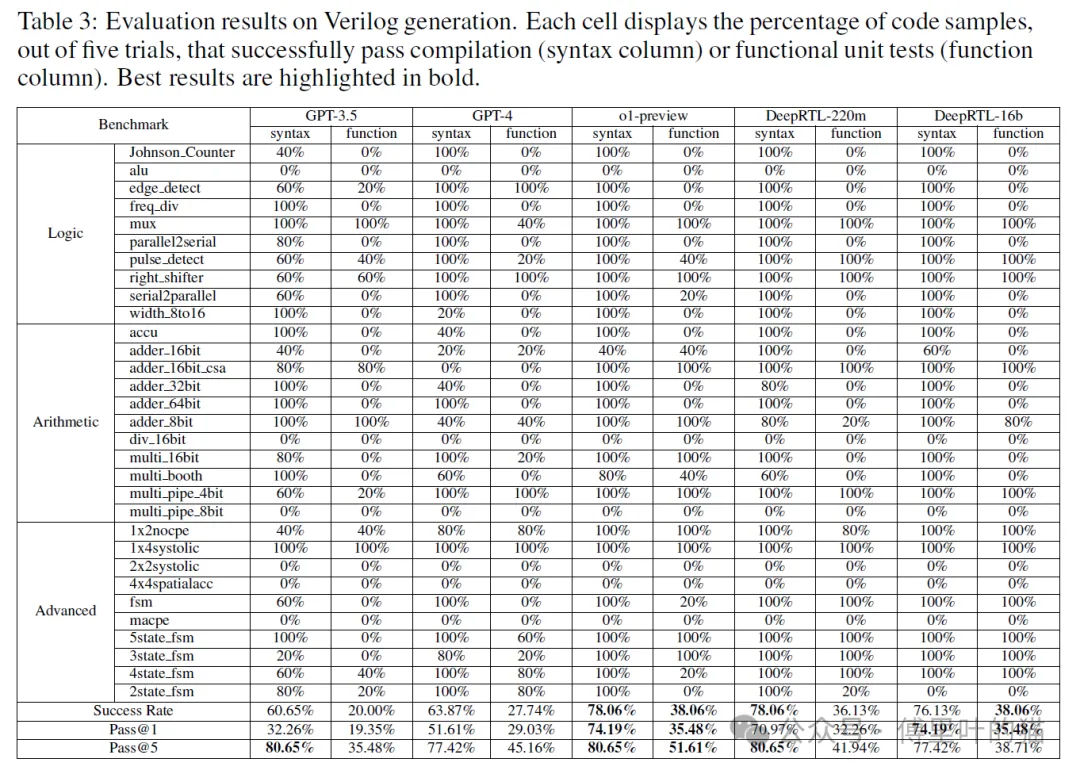

5.3 Verilog生成

鉴于CodeT5+和DeepRTL-direct在Verilog理解任务中表现不佳,我们的比较主要聚焦于GPT系列模型。如表3所示,OpenAI的o1-preview(专为复杂编程任务设计的最新模型)在所有指标上均表现最佳。尽管如此,我们的DeepRTL模型在多项指标上与o1-preview表现相当,并在语法正确性、Pass@1功能准确率和整体功能成功率上显著超越GPT-4。值得注意的是,DeepRTL在成功案例中生成的代码准确率极高,通常能在5个生成样本中达到100%通过率,这证明了其在实践中的可靠性。此外,考虑到OpenAI的模型得益于庞大的参数量和多样化的预训练数据,我们规模更小的DeepRTL模型的表现尤为突出。

6. 总结

在本研究中,我们提出了DeepRTL,这是一种新颖的统一表示模型,能够同时实现Verilog代码理解(从代码生成自然语言描述)和代码生成(从自然语言生成Verilog代码)。该模型基于精心构建的多层次数据集进行微调,该数据集包含行级、块级和模块级的Verilog代码描述,既有详细实现说明,也有高层功能描述。

DeepRTL不仅弥补了以往方法仅关注Verilog代码生成的不足,还确保了Verilog代码与自然语言之间的强语义对齐。此外,我们建立了首个评估大语言模型(LLM)Verilog理解能力的基准。为了克服传统指标(如BLEU和ROUGE)仅能衡量词汇重叠的局限性,我们采用嵌入相似度(Embedding Similarity)和GPT评分(GPT Score)来评估模型的理解能力。这些指标能更准确地衡量描述的语义相似性,从而更好地反映生成描述的精确度。

通过采用课程学习(Curriculum Learning)策略,DeepRTL在Verilog理解和生成任务上均表现出卓越性能。具体而言:

在Verilog理解任务中,它在所有评估指标上均超越当前最先进的LLM(如GPT-4);

在Verilog生成任务中,其语法正确性和功能准确性与OpenAI的o1-preview模型相当。

论文下载:

链接: https://pan.baidu.com/s/1fPiCfDuFBhRjkNXeOazDwA

提取码: u6un