文章来源:傅里叶的猫

好久不写FPGA的文章纯技术文章了,这篇文章我们写一个比较硬核的。

本文要介绍的,是合肥喆思电子推出高性能CoaXPress 2.1 & Over Fiber Bridge Device/HOST IP核。

在工业自动化与智能制造飞速发展的今天,视觉检测领域对相机的分辨率,帧率,延迟提出了更高的要求,高速、稳定、低延迟的图像传输技术成为机器视觉系统的不可或缺需求。

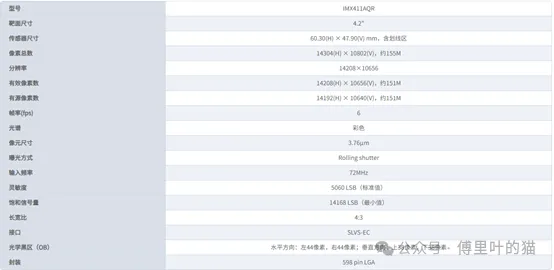

在面板/电池等Mura缺陷检测领域,更高精度检测要求靶面更大的传感器比如imx411,此传感器在全分辨率(14304x10802),12bit,6.3fps 模式下有效数据率达到11.7Gb/s,使用了SLVS-EC 8lane高速接口传输,在主控芯片FPGA 完成ISP处理后,需要快速把帧图像送到后端进行缺陷算法处理,此时如果用USB 口,网口或camerlink传输,速度是满足不了要求的。

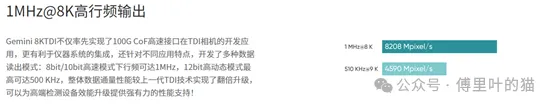

在半导体晶圆检测领域,线扫传感器的速率越来越高,数据量越来越大,普通数据传输接口难于满足数据带宽要求。比如相机厂商tucsen推出的最新的TDI 线扫相机,在8K分辨率下行频达到1MHZ,数据率达到恐怖的8208Mpixel/s,如此大的数据量也只能通过采集卡的PCIe Gen3x16或者Gen4x8接口送到服务器进行处理,但是相机如何把数据率送到采集卡呢?

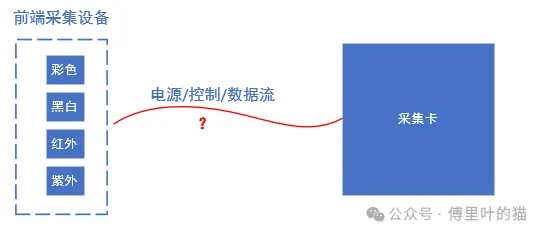

在多视频源场景下,比如彩色,黑白,红外,紫外等传感器集一体的前端产品,如何用最简单的物理连接实现电源/控制/视频流三合一?

在空间有限/低温/高辐射等特定环境下,高帧率相机与采集卡或者电脑需要远距离放置,还需要实时观看图像,此时使用哪种数据传输比较合适呢?

为了应对以上情形,日本工业成像协会(JIIA)在2011年正式发布CoaXPress (简称CXP)高速视觉传输标准,目前标准最新版本为2.1版本。CXP和其他标准相比具有以下优势:

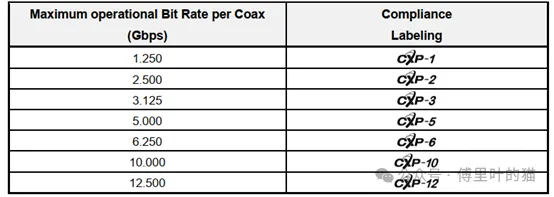

CXP标准目前规定了以下几种速率:

通过同轴电缆可实现电源/控制下发/视频数据流上传,其中:

每个同轴电缆链路可满足24V/13W的功率需求,多链路可满足前端采集设备功耗要求

每个同轴电缆链路最大实现12.5G速率,x2,x4可实现25G/60G速率

可实现多视频源的链路聚合

更精确的trigger控制

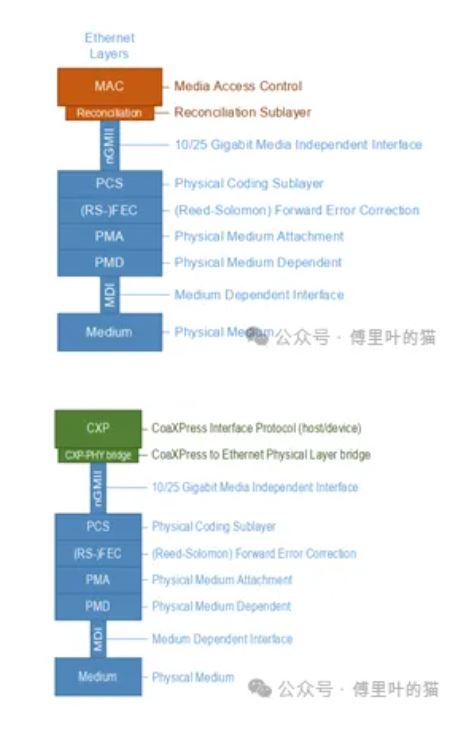

此外为了应对更高速率(25G),更远距离的场景,CoaXPress引入了基于光纤的物理传输媒介(CoaXPress-over-fiber),利用以太网数据链路层和物理层的接口nGMII、与CoaXPress数据层和物理层接口具有近似性的特点,将CoaXPress的数据层通过转换,链接到以太网的物理层,实现CoaXPress的数据在以太网光纤上的传输.

左边是以太网物理层结构,右图是CoaXPress-over-fiber物理层结构

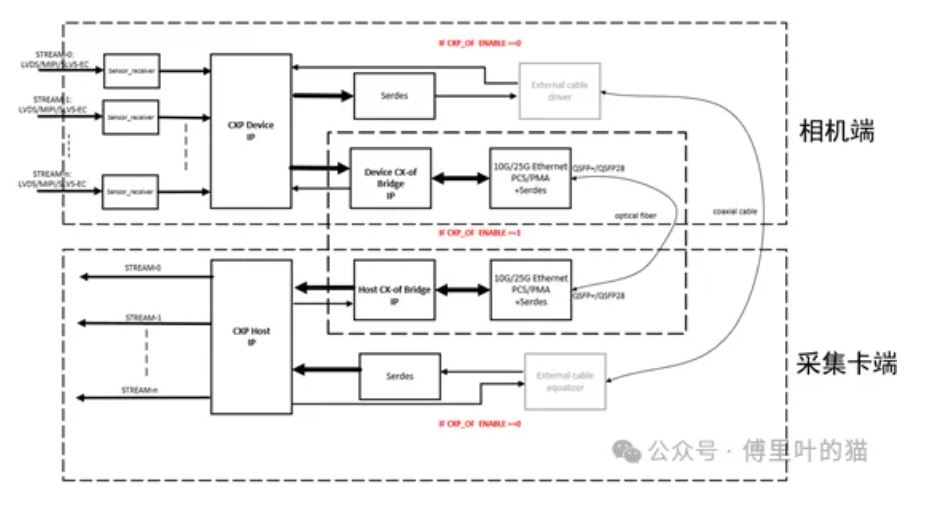

合肥喆思电子凭借深厚的FPGA技术积累,正式推出符合CoaXPress 2.1和CoaXPress over Fiber Bridge Protocol 1.1标准的高性能HOST/DEVICE IP核,可适配AMD/ALTERA 主流FPGA 平台。基于喆思CXP HOST/DEVICE IP 搭建的高速视频传输系统架构如下:

HOST/DEVICE IP具有以下特点:

支持CXP1-CXP12所有速率,可动态切换.

低速支持20.83Mbps和41.6Mbps.

支持option high speed upconnection(和low speed upconnection二选一)

数据包CRC 校验.

最高支持8lane 传输,Host最大支持外接8个图像设备.

前端图像设备最大支持4个stream.

支持10G/25G over Fiber Ethernet.

AXILite总线控制.

输出方式支持Vsync/Hsync和Axi_stream.

DEVICE IP 已和市面上常见的采集卡适配。

HOST IP已在AMD XCKU060 FPGA上适配bopixel ,tucsen,vieworks,大华等相机。

CXP12 x4:

CXP over fiber Ethernet 10Gx4:

CoaXPress Host/Device IP 核心价值,助力客户实现技术突破与产品升级

1.赋能自研采集卡,集成高效视频处理算法

提供灵活可扩展的FPGA IP核,支持客户在自研采集卡中无缝集成降噪、锐化、HDR、AI检测等图像算法,显著提升图像质量与处理效率。

2.多模态图像采集,一站式融合处理

支持黑白、彩色、红外等多光谱相机的同步采集与协同处理,实现多源数据的高效整合,满足复杂场景下的视觉分析需求。

3.加速产品研发,缩短上市周期

提供标准化协议栈与成熟参考设计,大幅降低相机与采集卡厂商的开发门槛,助力客户快速完成产品验证与量产部署。