Xilinx A7 芯片内部结构分析(2)——存储单元

judy 在 周五, 12/07/2018 - 09:46 提交

上一篇中提到了SLICEL和SLICEM都可用作ROM,后者还可以作为分布式RAM(Distribute RAM,DRAM)。本篇主要总结的是块状Memory(Block Memory),实际上就是FPGA内部独立于逻辑单元的专用存储器,更像是一种硬核。

1. 基本结构

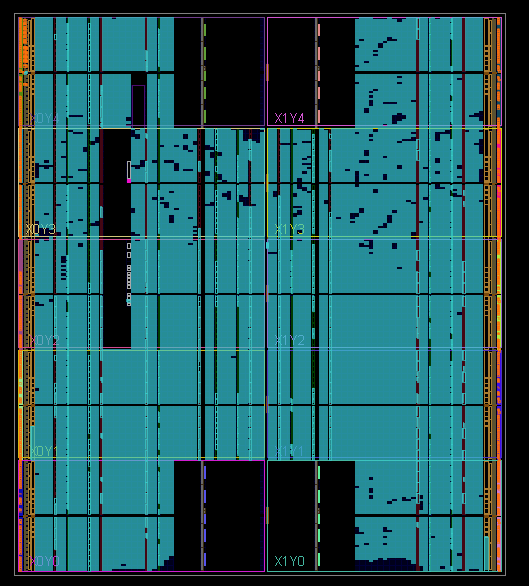

如下图所示,一个Block Memory的大小为36KB(RAMB36E1),由两个独立的18KB BRAM(Block RAM,RAMB18E1)组成。因此一个36K的Block Memory可配置成4中情形:

为什么不能配置成两个18KB的FIFO呢?因为一个Block Momery中间有一个叫FIFO Logic的结构,它用于生成FIFO控制信号,包括读/写地址等,由于它只有1个且不能共享,所以最多只能配置一个FIFO。