BUFGMUX的使用

judy 在 周一, 07/11/2022 - 10:00 提交

BUFGMUX可能使用Xlinx FPGA器件的都有了解,但从使用角度考虑,做FPGA产品开发时,可能使用比较少,但做FPGA原型验证可能就比较多了。

BUFGMUX可能使用Xlinx FPGA器件的都有了解,但从使用角度考虑,做FPGA产品开发时,可能使用比较少,但做FPGA原型验证可能就比较多了。

在5G无线、卫星通信、雷达探测、航天测控等复杂系统设计中,FPGA工程师扮演着重要角色。对于一个FPGA团队来说,需要根据项目需要完成产品的设计和验证,保证项目的交付。

虽然 FPGA 可使用 Verilog 或 VHDL 等低层次硬件描述语言 (HDL) 来编程,但现在已有多种高层次综合 (HLS) 工具可以采用以 C/C++ 之类的更高层次的语言编写的算法描述

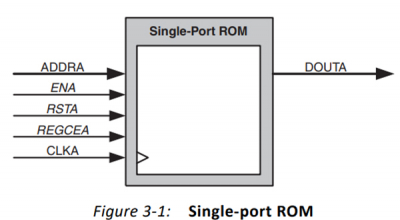

本文介绍一种在FPGA开发中非常常用的存储类 IP 核——ROM 的使用方法。

本节我们介绍以下知识点:SelectIO资源概述及结构,SelectIO管脚通用设计指导。

在有些情况下,开发人员只有综合后的DCP文件和对应的约束XDC及各个IP,并没有综合之前的code,这种情况下vivado可以通过tcl脚本跑完实现并得到bit。

本人比较喜欢Xilinx家的东西,这里就讲一讲Xilinx家的MIPI方案。这里以普通7系列作为讨论的对象

本文将对RAM IP核的各个关键因素做详细的讲解。

xkISP 是基于 Xilinx HLS 的开源图像信号处理器 (ISP)。xkISP由复旦大学VIP实验室和阿里巴巴DAMO CTL实验室联合开发

case语句可以说是我们在FPGA开发中使用频率非常高的一条语句。同时,Verilog还提供了语句 casex 和 casez供我们使用。