DCI与内部参考电压

Xilinx FPGA提供了DCI(Digitally Controlled Impedance)技术,包括两个功能:(1).控制驱动器的输出阻抗;(2).为驱动器或发送器添加一个并行端接,在传输线上得到精确的特征阻抗匹配,以提高信号完整性。DCI会主动调整I/O bank内的阻抗,以调整放在VRN和VRP管脚之间的外部精准参考电阻,这样可以补偿由于工艺变化、温度变化和电源电压抖动引起的I/O阻抗变化。每个I/O bank内都有两个复用引脚来控制该bank内所有I/O的阻抗或并行端接值。

带有差分输入缓冲区的单端I/O需要一个参考电压Vref,可以使用专用的Vref管脚为每个I/O bank提供参考电压。另外也可以使用INTERNAL_VREF约束来生成内部参考电压,这样PCB上就不需要为Vref提供电源线,也可以释放Vref管脚作为通用I/O使用。每个bank都可以设置一个可选的内部参考电压。

Ug471和ug571分别介绍了7系列和UltraScale系列中DCI和INTERNAL_VREF的详细信息。本文将介绍在Vivado中设置与之相关的DCI_CASCADE和INTERNAL_VREF属性。

创建DCI_CASCADE约束

DCI_CASCADE约束可以将多个相邻的I/O bank级联在一起,共享DCI参考电压。其中包含DCI参考电压的称作主bank;级联的其它I/O bank称作从bank。每个级联链都必须有一个主bank和至少一个从bank。

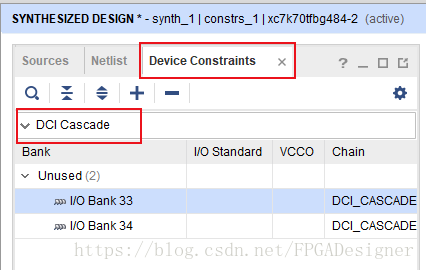

在Device Constraints窗口中,选择DCI Cascade:

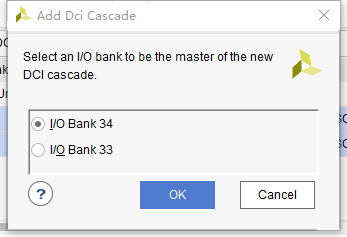

Unused文件夹中显示了未添加到DCI级联链中的I/O bank,选择需要添加的所有bank,右键->Add DCI Cascade创建级联链,弹出如下窗口:

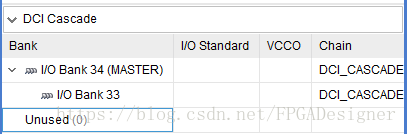

选择主bank,点击OK则创建好级联链,显示在窗口中:

或者直接将某一bank拖动到另一bank上也可以完成相应操作。设置DCI_CASCADE约束对应的XDC命令如下:

set_property DCI_CASCADE {33} [get_iobanks 34]

get_iobanks选择的为主bank,{}中的是添加到级联链中的从bank,以空白为间隔。上述创建的约束需要点击保存,如果设计已经有了XDC约束文件,约束命令会添加到文件末尾。

创建INTERNAL_VREF约束

使用INTERNAL_VREF约束可以生成FPGA的内部参考电压。这样就不需要在PCB上提供Vref电源线,且可以释放Vref管脚作为通用I/O使用。

在Device Constraints窗口中选择“Internal VREF”,列出了该芯片支持的内部参考电压,NONE文件夹中的I/O bank表示没有设置INTERNAL_VREF约束。

创建INTERNAL_VREF约束,只需要将I/O bank拖到对应参考电压的文件夹中即可;拖到NONE中表示撤销参考电压设置。该设置对应着约束命令,需要保存到XDC约束文件中,示例如下:

set_property INTERNAL_VREF 0.75 [get_iobanks 14]

set_property INTERNAL_VREF 0.675 [get_iobanks 15]

文章来源:FPGADesigner的博客

*本文由作者授权转发,如需转载请联系作者本人