利用ZYNQ验证算法的一大优势在于,可以在上位机发送指令借助CPU的控制能力和C语言易开发特点,实时配置算法模块的工作模式、参数等对来对其算法模块性能进行全面的评估。最重要的是无需重新综合硬件模块。

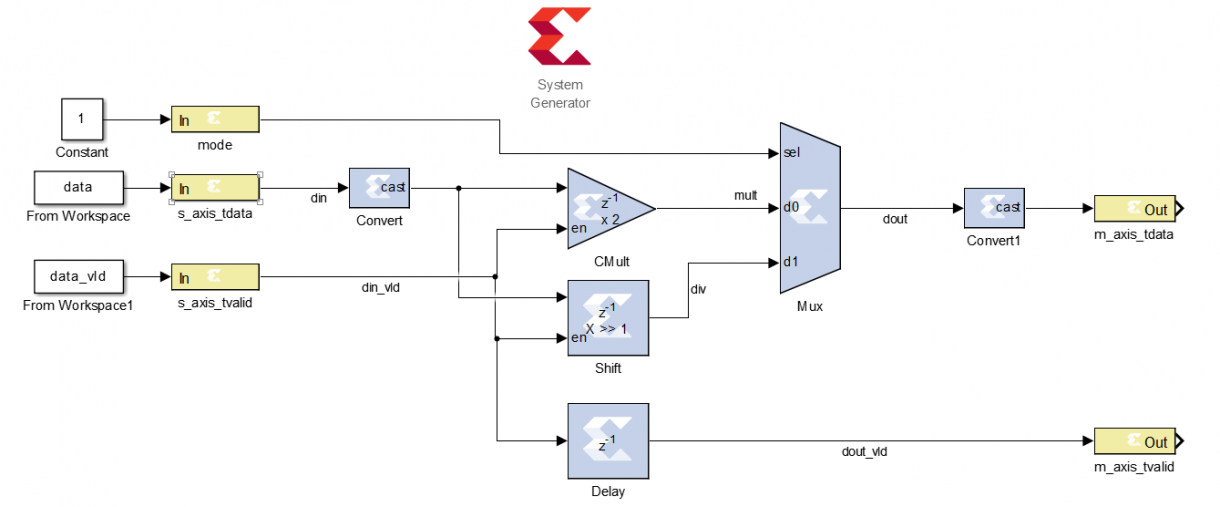

接着上篇该系列博文,在sysGen中设计模块功能为:根据模式选择输入,来完成乘2或除2两种运算,0乘1除。

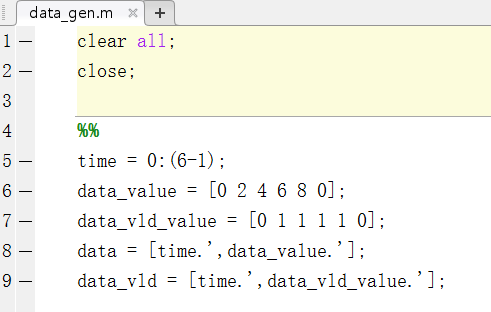

测试激励选用From Workspace模块,从MATLAB工作空间导入数据。利用MALTAB脚本可以非常容易地生成任意数据集,极大体现了sysGen开发的优势。

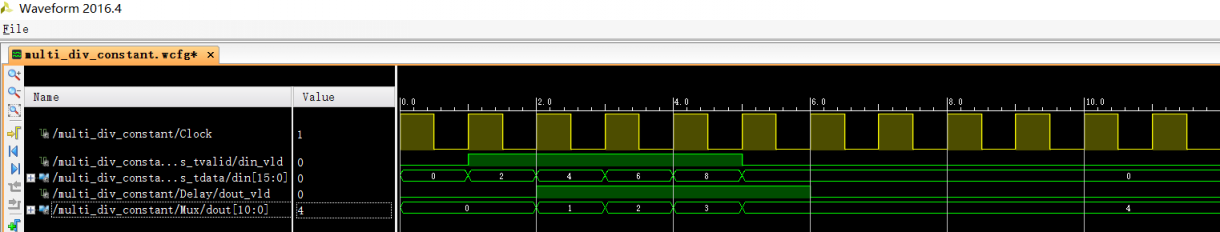

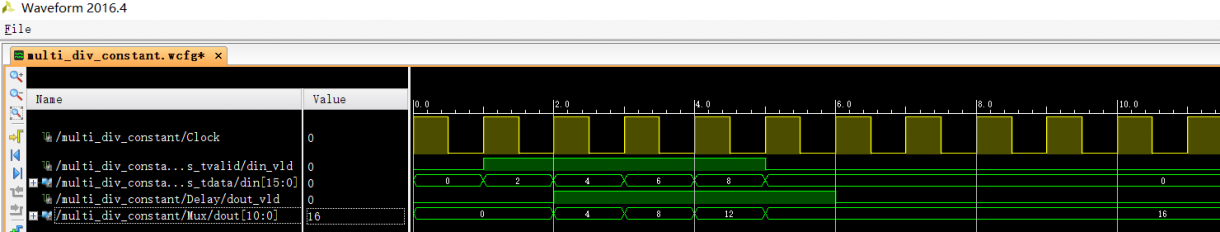

设计完成调用xilinx waveform viewer,两种运算行为仿真波形如下:

功能验证无误,关键的一点是让mode端口以AXI总线形式传递数据。

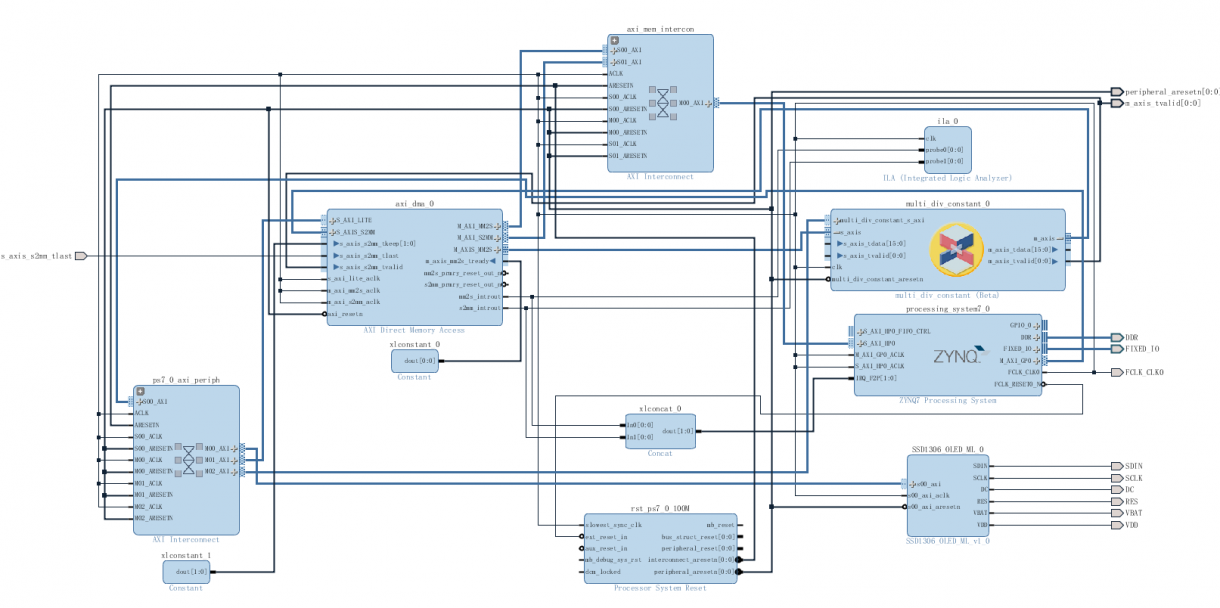

现在将sysGen算法子系统生成IP核,并导出到IP Integrator中作为CPU外设。

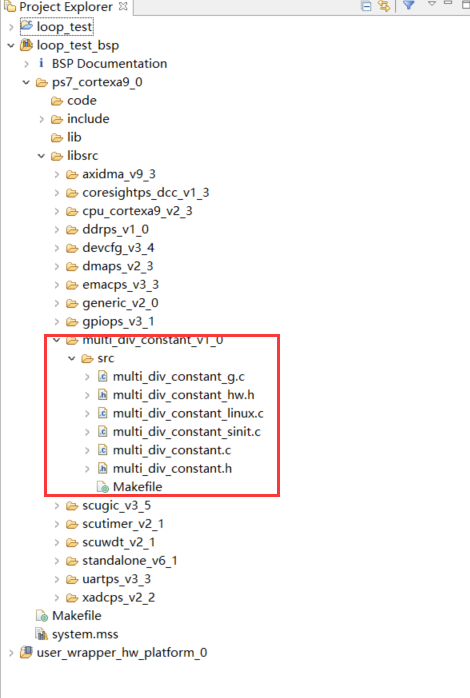

可以看到multi_div_constant模块多出一个multi_div_constant_s_axi总线接口集。该接口遵循AXI-Lite总线规则,用于配置IP核内部控制寄存器。硬件系统设计完毕,导出硬件启动SDK。当新建工程后,能看到AXI总线驱动自动添加进来了。

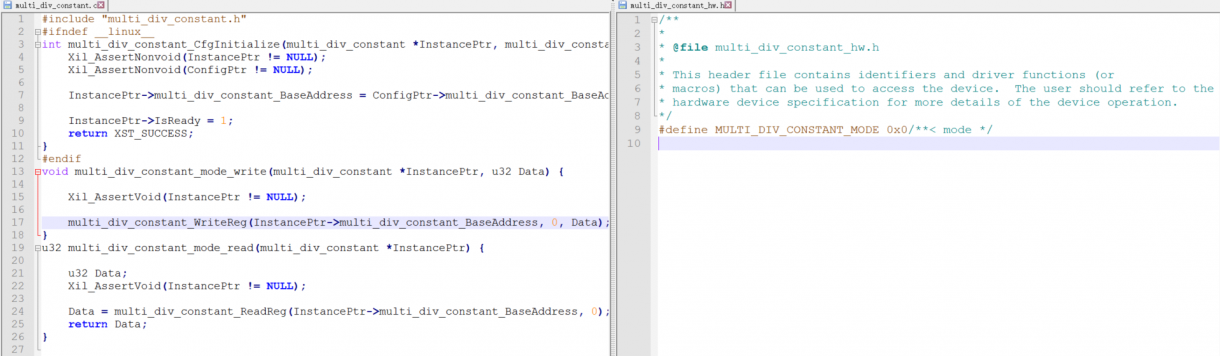

multi_div_constant_hw.h内部为AXI-Lite总线寄存器地址,multi_div_constant.c内是驱动函数的具体实现。

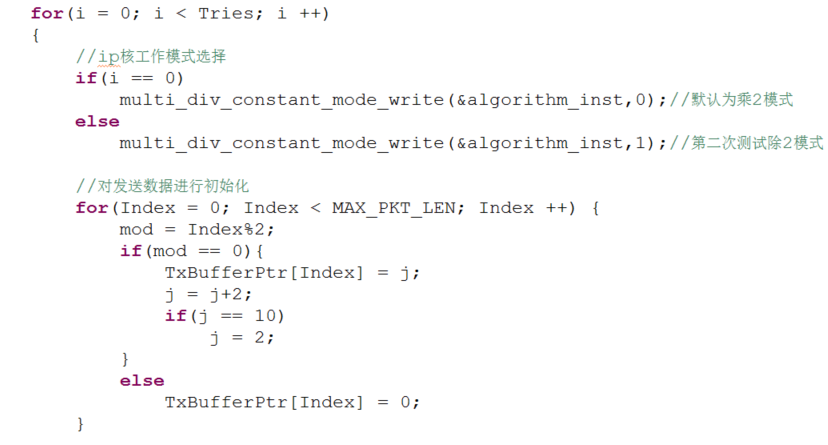

C代码对算法模块进行板级验证:

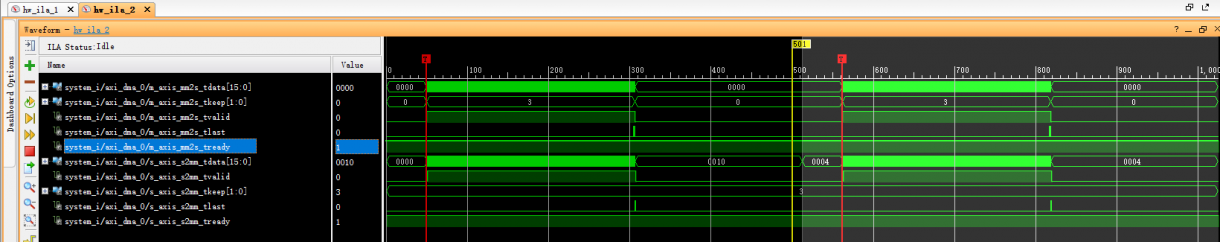

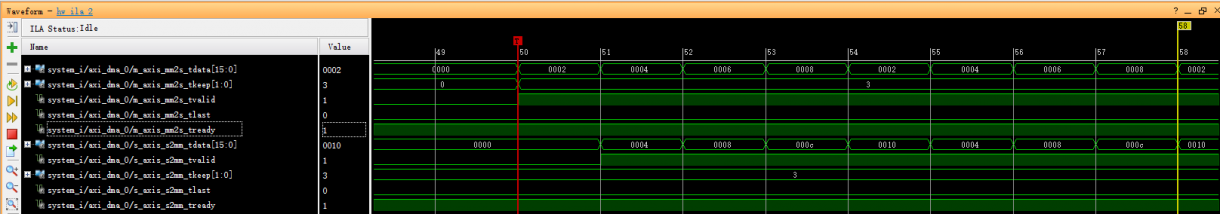

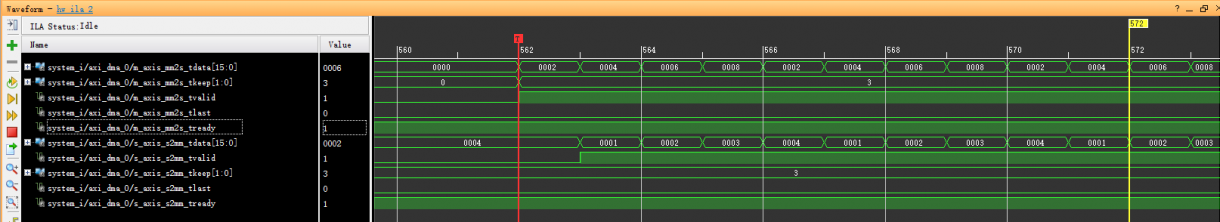

启动Debug,点击运行查看软件运行结果和AXI-Stream总线时序波形。

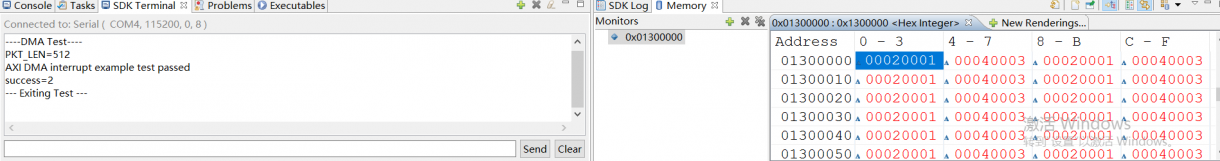

SDK中串口打印结果及Memory窗口查看DDR接收缓存绝对地址。

正确启动了两次DMA环回传输,第一次算法模块工作在乘2模式,第二次则除2.C代码中测试返回数据与生成测试数据关系无误,DDR绝对地址数据也别正确更新。