作者:做但不能忘思考,来源:FPGA2嵌入式

项目的设计初期,我们需要选型FPGA后进行FPGA原理图设计,FPGA的原理图设计和单片机的原理图设计有很大的区别:单片机的外设是固定的引脚,我们只需要根据数据手册确定各个外设的引脚就行,但是,FPGA却大不相同同,引脚外设既灵活又有很多约束条件,灵活是不同的UART/SPI等外设引脚的确定可以根据需求改变,很多约束条件指:配置引脚、时钟等有很多约束条件。下面来介绍不是常规的通过大量单一的查阅数据手册来初步进行引脚分配,而是在Vivado中新建IO Planning工程来初步引脚分配,这样会大大提高开发效率,目前只在Vivado中发现此功能,现在分享给大家。

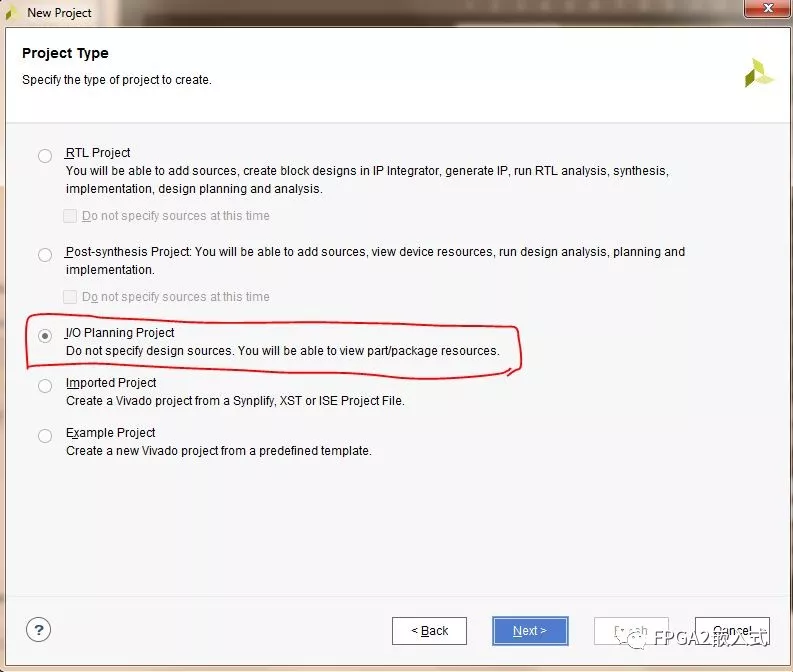

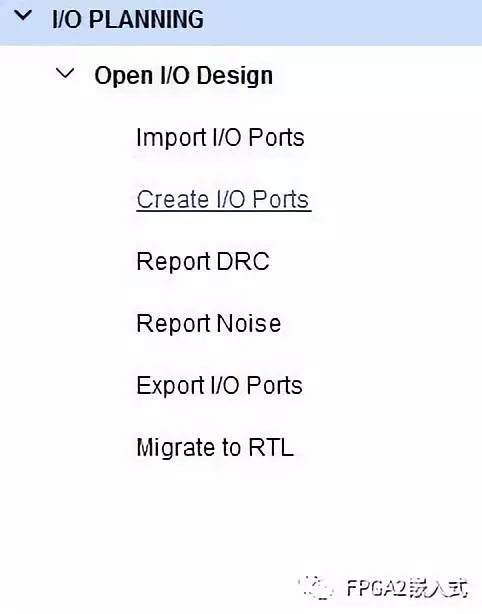

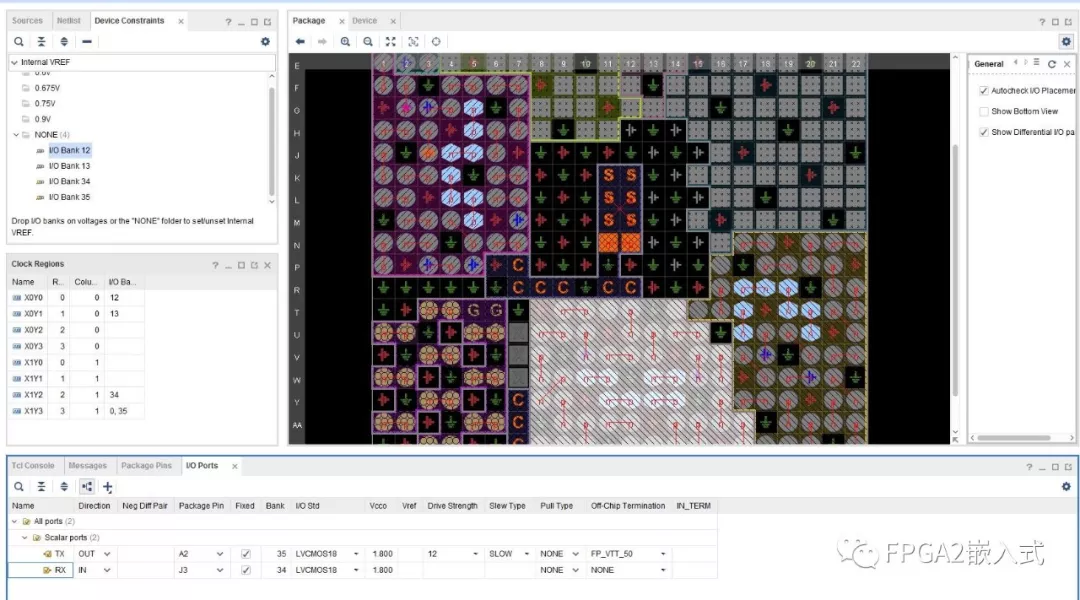

如上图所示,打开Vivado后,新建工程,选择IO Planning工程,IO Planning工程不需要任何设计的源文件就可以查看FPGA的引脚资源。当然,其它几项就是新建RTL工程、导入以前的XST、ISE工程文件、新建例程工程。接下来,就是:

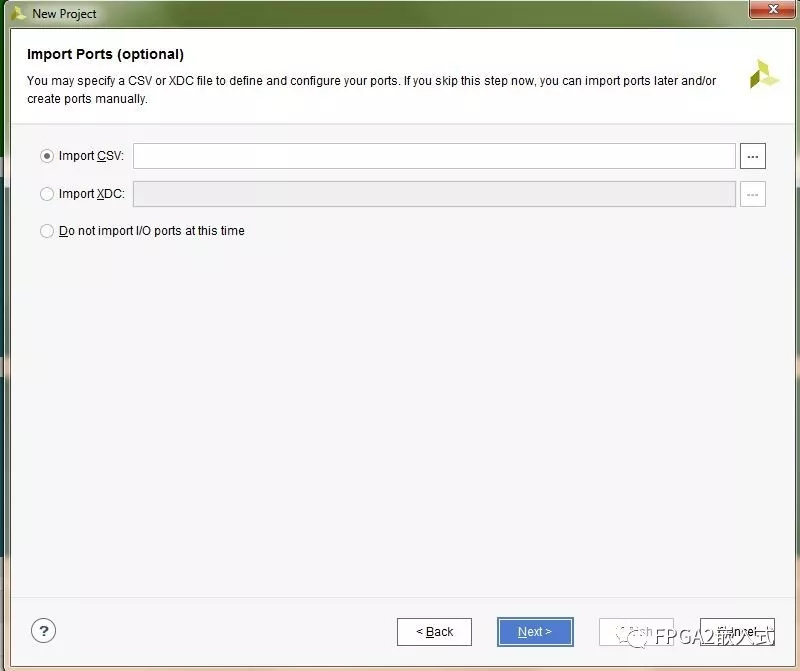

可选的导入IO分配文件,可以是CSV或XDC格式的文件,其中,CSV和XDC文件可以由Candance原理图设计软件直接导出后使用,如果你一直是手动的编写CSV或XDC文件,那就太OUT了。接着,自然到了型号选择了:

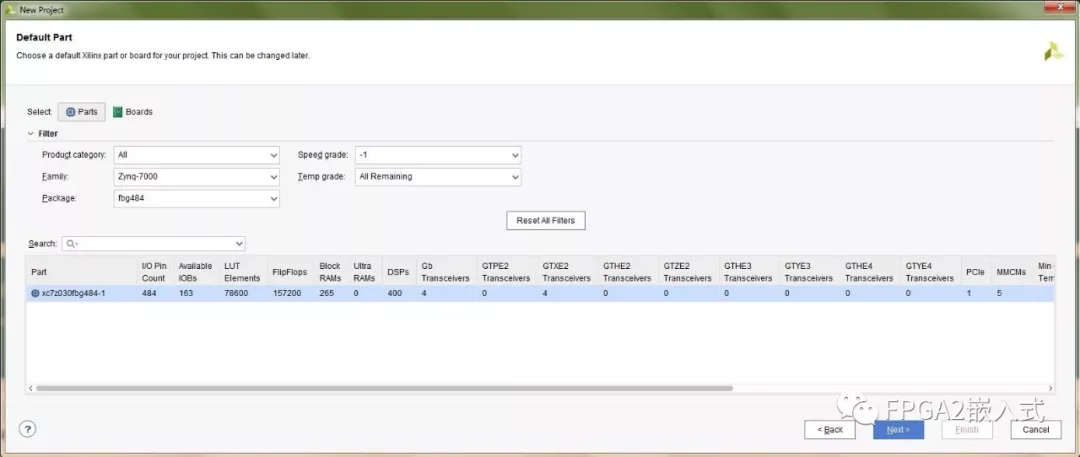

在这里,你可以选择最右侧的开发板型号,也可以选择Part,具体的FPGA的型号,选择完后,我们可以很清晰的看到该型号的资源列表:包括IO数、可用的IO数、内部BRAM大小、时钟资源等。最终确定后,我们可以很直观的看到FPGA的引脚视图,如下图:

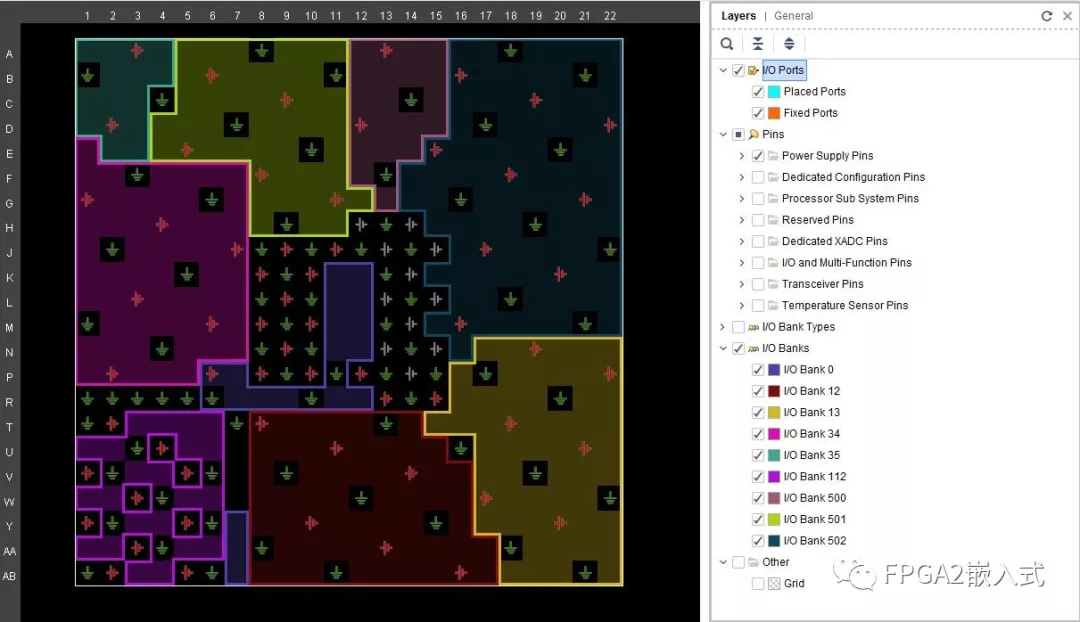

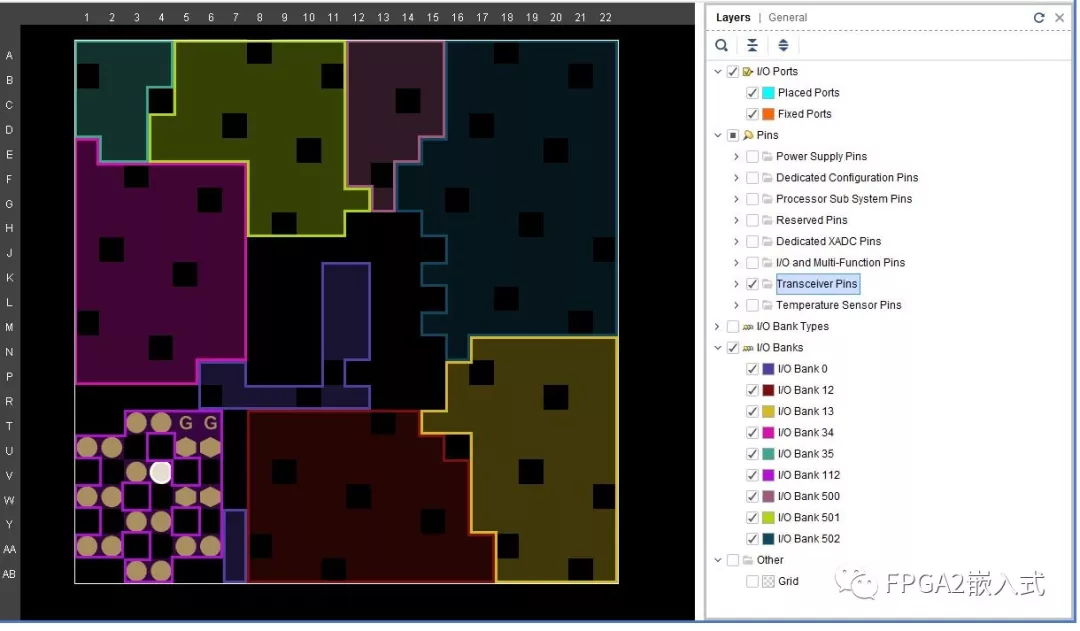

下面,我们看看到这里,他有那些用处,查看不同属性的引脚分配,指导PCB设计,如下图:只查看各个BANK及电源引脚的分布图:

查看Transceiver Pins的分布图:

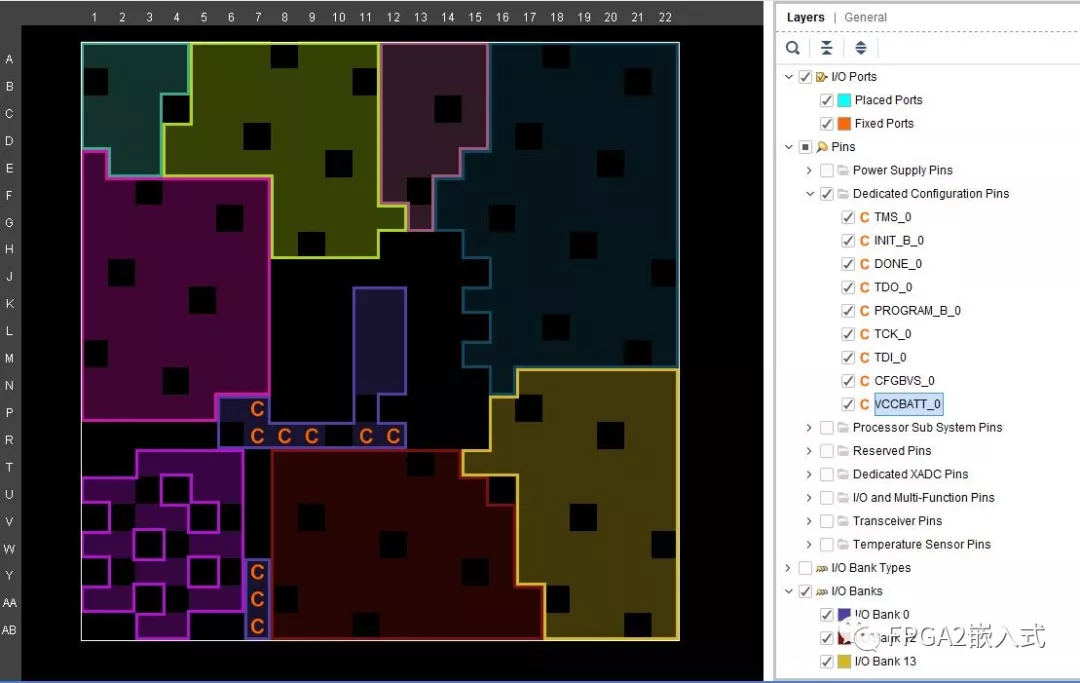

专用的配置引脚分布图:

通过右侧的筛选框来筛选查看某类引脚分布图。当然除了这个功能,还可以根据导入的CSV或XDC文件来生成顶层文件来验证引脚分配的合理性,检查DRC等:

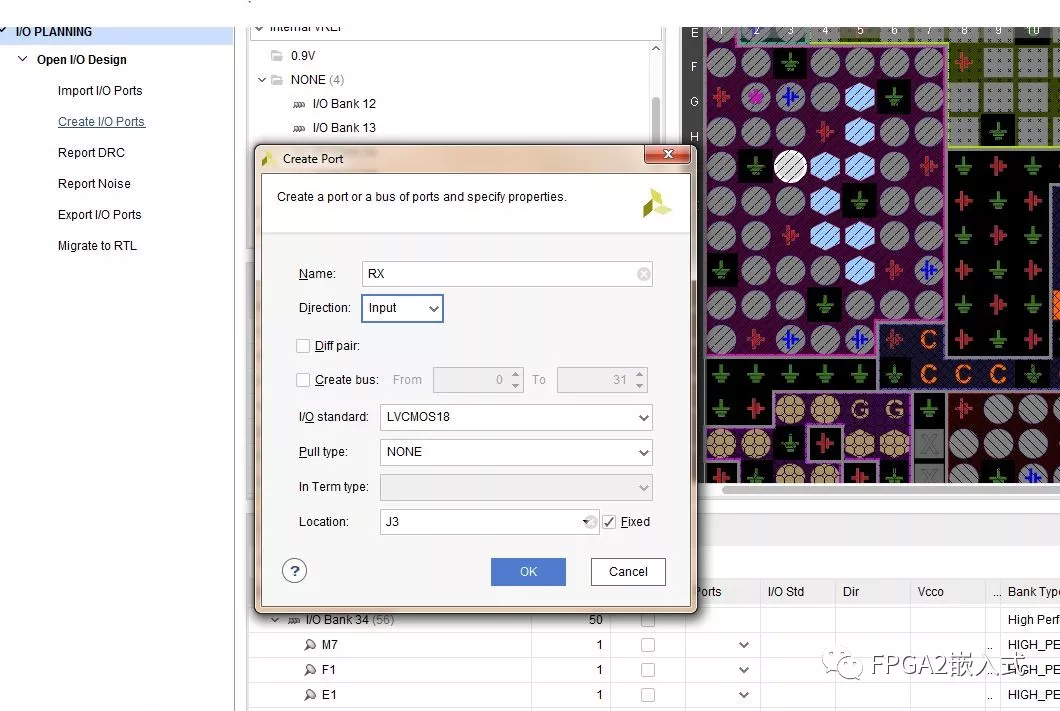

同样,可以手动添加分配引脚,并查看差分对引脚情况。

总之,通过IO Planning工程可以很好的帮助我们设计原理图、PCB和项目选型评估。

文章转载自: FPGA2嵌入式