作者:圆宵,来源:FPGA那点事儿

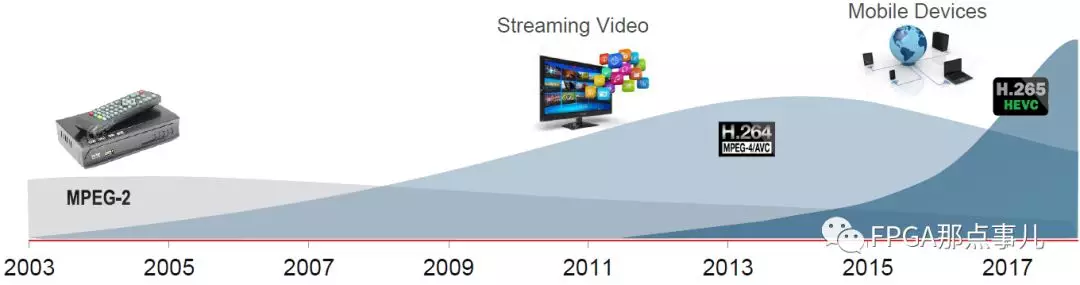

随着视频应用场景和内容越来越丰富,对网络传输,存储,和AI智能分析带来了越来越高的需求和挑战。以一路FHD@60fps视频为例,其RAWDATA的带宽约为3Gbps;到了4K@60fps,带宽大约为12Gbps;到8K,带宽更是会到48Gbps。这样大的数据量,如果不进行压缩是没有办法进行传输和存储的。因此,从早年的MPEG2,到当下被广泛采用的H.264,H.265,再到VP9,AV1以及未来的VVC,各种各样的视频编解码标准被提出来。每代都比之前在编码效率上有提升,付出的代价就是更大的编码复杂度。

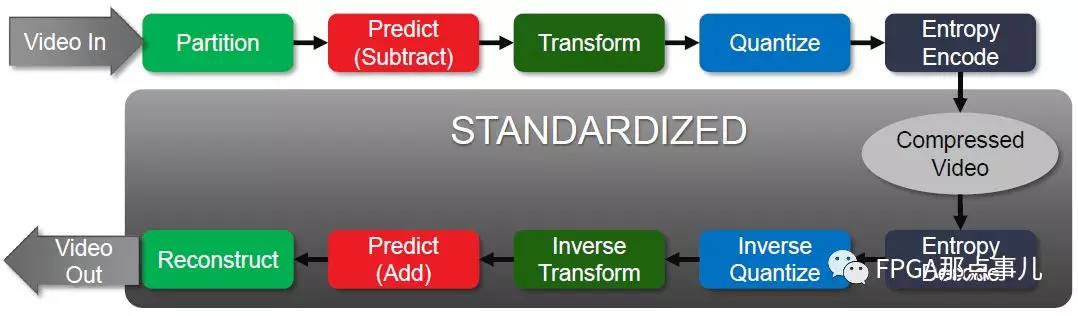

不管编解码标准变得如何复杂,它们的基本技术思想都是类似的。通过帧内压缩和帧间压缩,同时压缩空间冗余度和时间冗余度。对于编码来说,都要经过预处理,运动估计,变换,量化,熵编码这几个基本步骤;解码过程则跟编码过程完全相反。

这里有几点基本概念一定要注意下:

1. 编解码标准一般只定义解码过程,而不定义编码过程。如何从原始图像得到压缩后的码流,正是各家Codec存在差异显神通的地方。

2. 正因为标准只定义Decoder,所以对于给定的输入,任何Decoder的输出都是一致的,Decoder很少有能做差异化的地方。Decoder的难点是兼容各种各样的Profile输入。

3. Encoder通常会比Decoder复杂很多(5-10倍),计算量也大很多。每个Codec都会采用很多种差异化的算法。因此对于给定的视频原始输入,不同的encoder输出的码流都是不一样的,不过它们都符合标准。

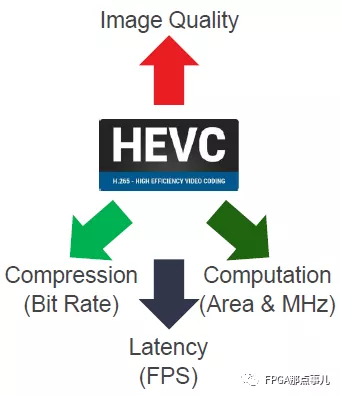

4. Encoder输出码流的图像质量,受很多因素相互制约和影响:Compression Ratio,Latency,ComputationComplexity。这三者往往是互斥的,不可兼得,只能根据实际的应用场景,选择合适折中的方式。

Xilinx的Zynq Ultrascale+MPSOC EV系列器件已将集成了H.264/265 的Codec硬核,可以同时支持最大一路4K@60fps视频的同时编解码。下章会有关于XilinxVideo Codec的更多介绍。

文章转载自:FPGA那点事儿